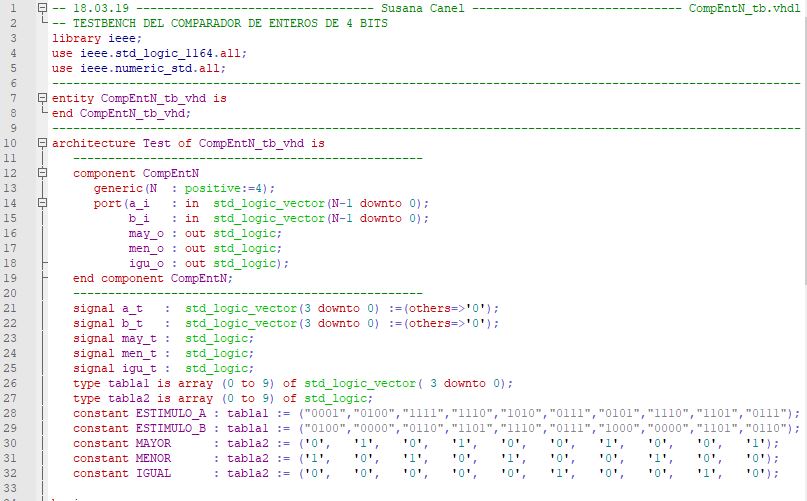

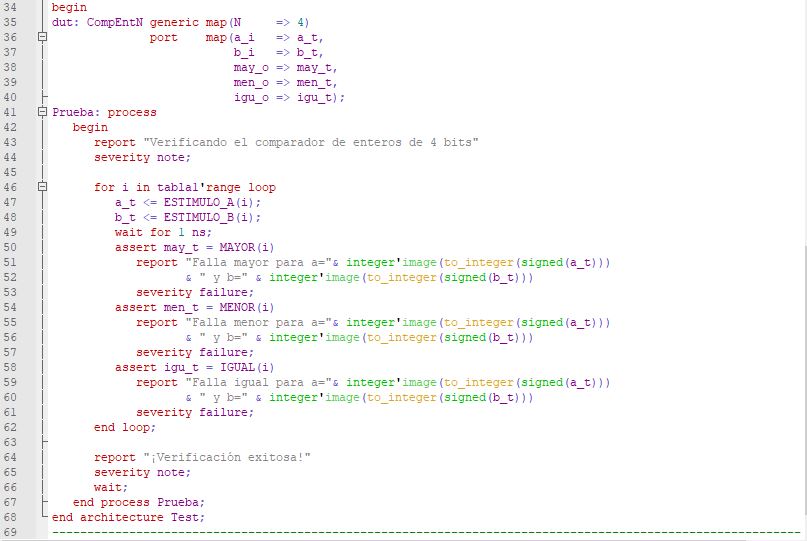

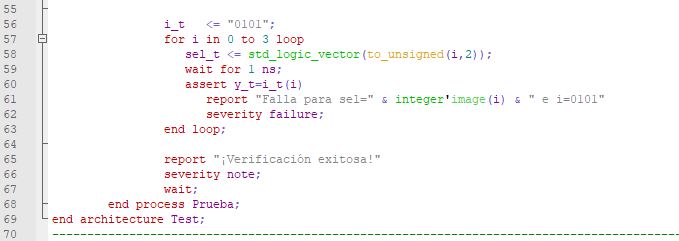

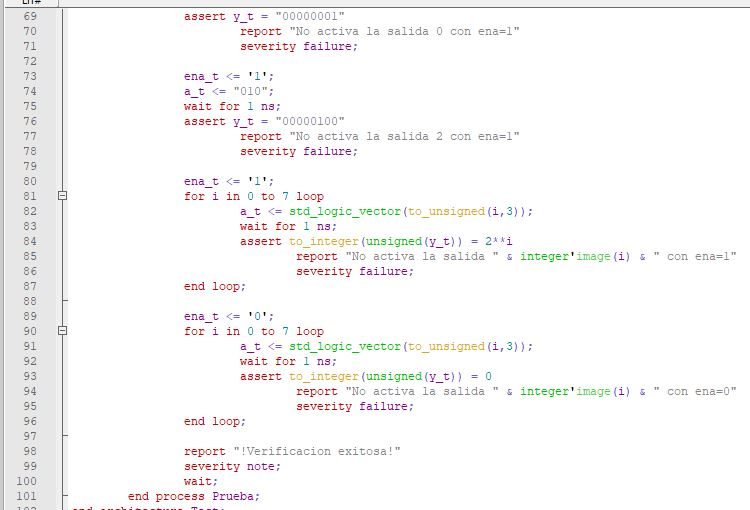

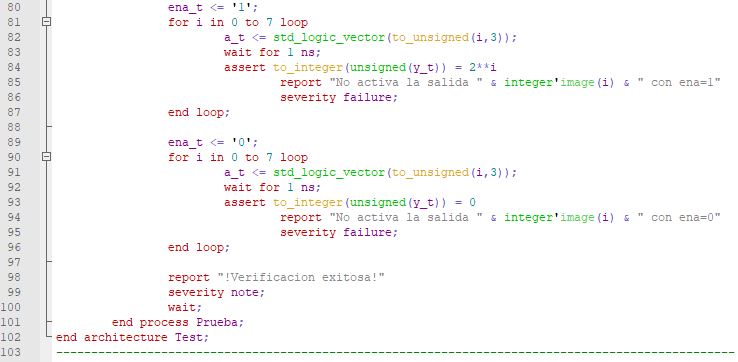

En este video te muestro un testbench para el comparador genérico de números enteros de N bits. Uso tablas para generar los estímulos de las entradas y también tablas (type … array) para generar las salidas esperadas, de manera que con un simple for…loop verifico los 10 casos que elegí como para cubrir todas las posibilidades. Uso los atributos ‘range e ‘image. Incluyo el package numeric_std para poder usar la función: to_integer.

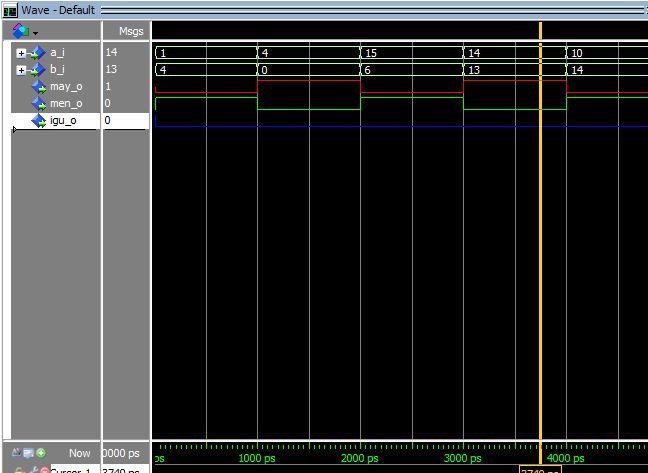

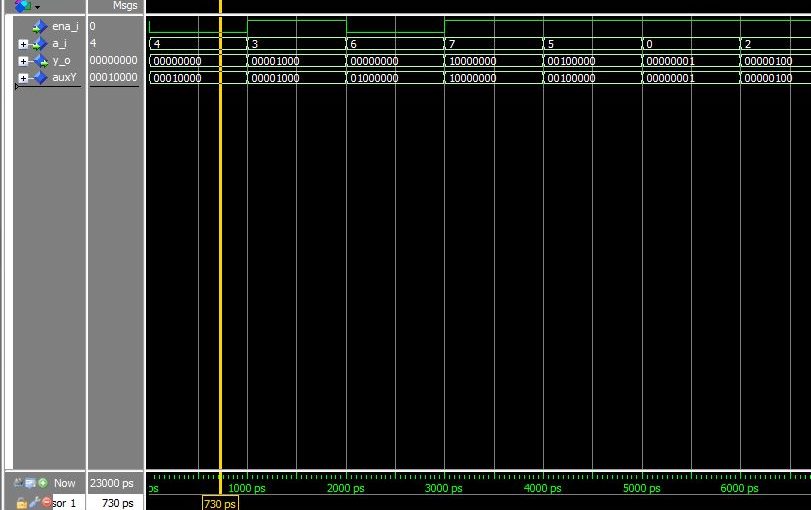

Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.