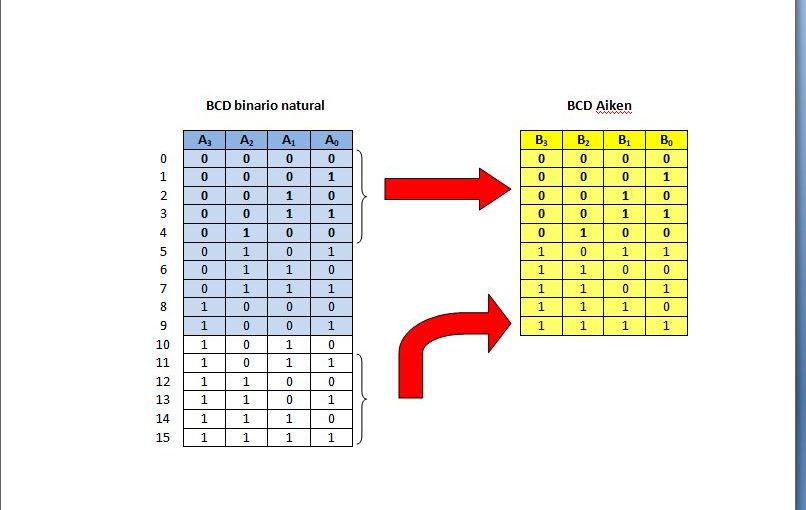

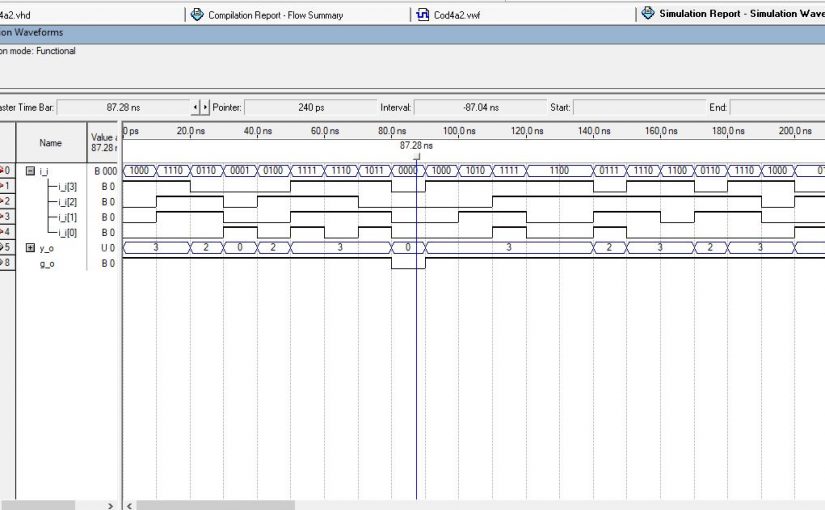

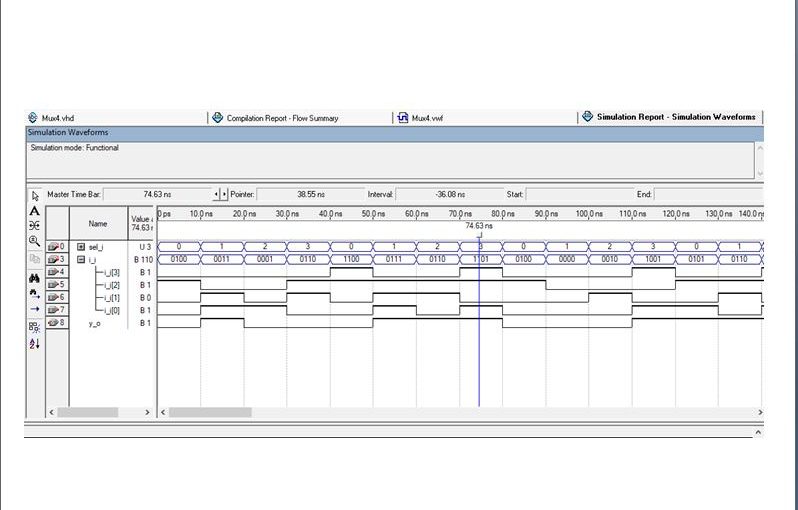

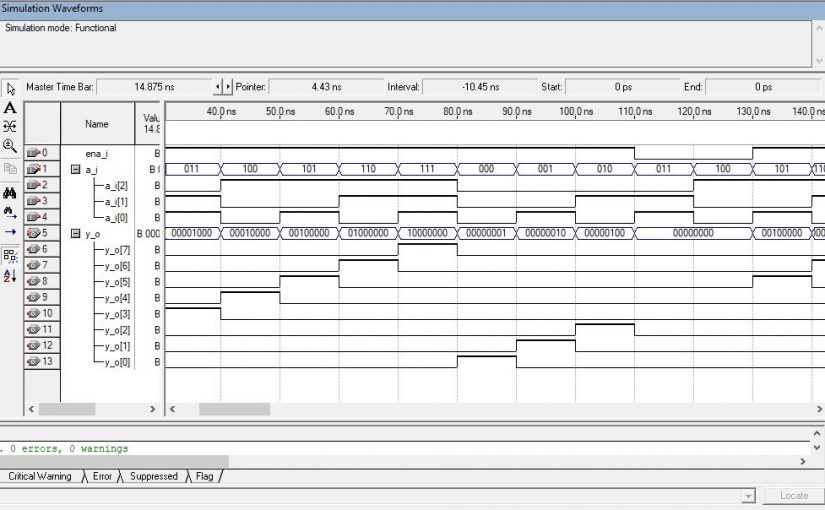

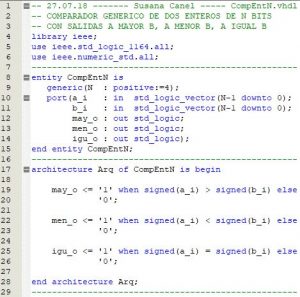

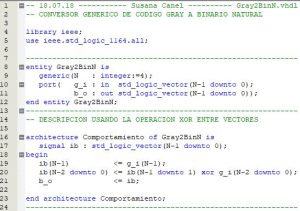

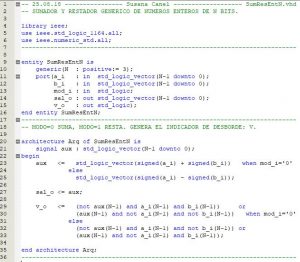

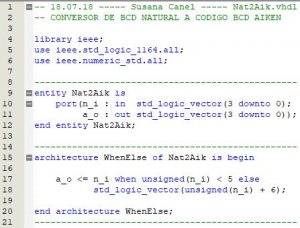

En este video te describo un conversor de código BCD binario natural a código BCD Aiken, usando operaciones aritméticas que no están permitidas para el tipo de datos std_logic y std_logic_vector, motivo por el cual tengo que usar el package numeric_std del IEEE. Este package incluye nuevos tipos de datos, entre ellos unsigned. Haciendo conversión de datos soluciono el problema. Primero cometo adrede un error para que veas cómo te avisa el compilador que no puede hacer operaciones aritméticas con el tipo de datos std_logic_vector. Una vez corregido, lo vuelvo a compilar y finalmente simulo para comprobar el correcto comportamiento. También te muestro dónde se encuentran los package en la instalación de Altera, en particular los dos que hemos usado:

std_logic_1164 y numeric_std

Los abro para mostrarte parte del contenido, por ejemplo los tipos de datos que usamos en esta descripción. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/