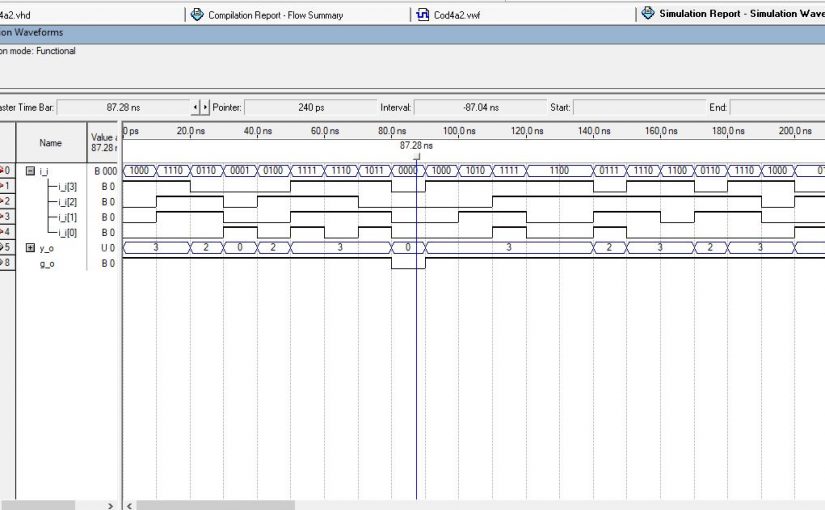

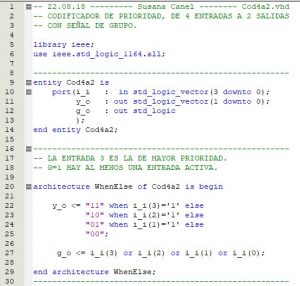

En este video realizo la descripción VHDL de un codificador de prioridad de 4 vías con señal de grupo. Explico las características de la sentencia when-else que uso. Posteriormente realizo la simulación usando el Quartus II, 9.1. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Etiqueta: dispositivos de propósitos generales

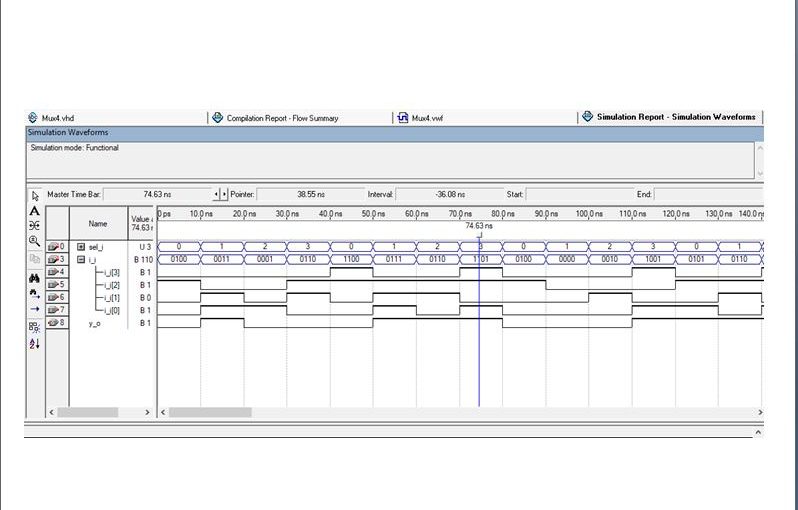

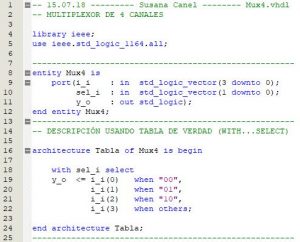

Lección 2.V10. Descripción y simulación de un multiplexor de 4 canales.

En este video te muestro la descripción de un multiplexor de 4 canales usando with-select para generar una tabla. Además adrede cometí un error en la descripción para mostrarte cómo lo informa el compilador. Posteriormente lo simulé usando el Quartus II, 9.1. y muestro cómo conviene elegir los estímulos de las señales. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

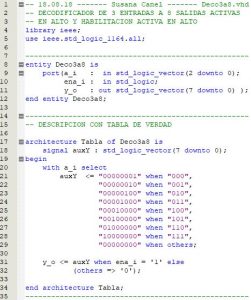

Lección 2.V7. Descripción de un decodificador de 3 a 8 con habilitación.

Con este video inicio la Lección 2, que corresponde a descripciones VHDL de dispositivos combinacionales de propósitos generales o MSI. Describo un decodificador de 3 entradas a 8 salidas activas en alto, con entrada de habilitación también activa en alto. Uso las sentencias with-select para generar la tabla de verdad y las sentencias when else para poner la condición de habilitación. Uso when-others para cubrir todos los casos y la expresión (others =>’0′) para generar un std_logic_vector en 0 sin tener que conocer la dimensión del vector (el software ya posee esa información). Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Lección 3. VHDL por comportamiento.

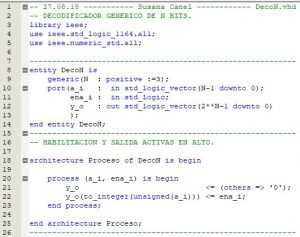

Circuitos combinacionales genéricos. En estos ejemplos complico algo la sintaxis pero para obtener grandes ventajas al describir dispositivos que no tienen limitaciones en la cantidad de bits, por eso se los llama “genéricos”. En los videos tendrás las explicaciones detalladas de cada descripción.

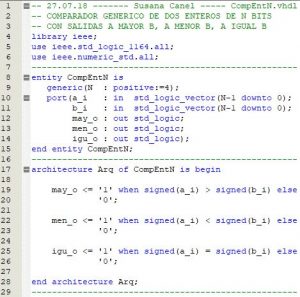

1. Comparador genérico.

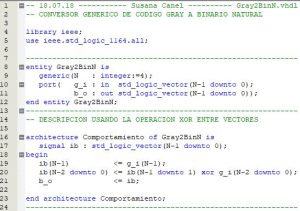

2. Conversor genérico de código Gray a binario natural.

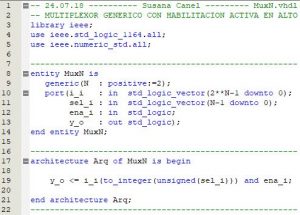

3. Multiplexor genérico de N canales.

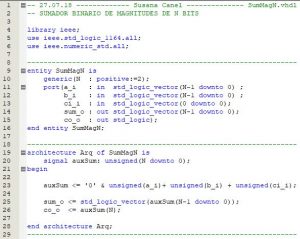

4. Sumador genérico de magnitudes.

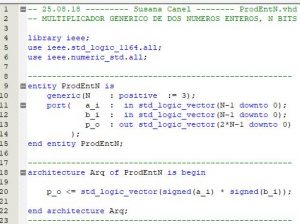

5. Multiplicador genérico de dos números enteros.

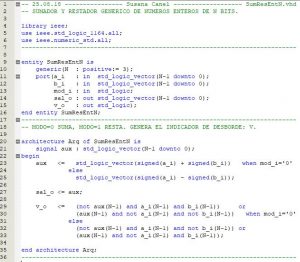

6. Sumador-restador genérico de números enteros.

7. Memoria tipo ROM usada para convertir binario natural a Gray, 4 bits.

8. Decodificador genérico con habilitación activa en alto.

9. Árbol de paridad, genérico, con salidas: paridad par e impar.

Lección 2. VHDL por comportamiento.

Circuitos combinacionales particulares. En estos ejemplos uso los diferentes estilos, en cada caso el más apropiado.

1. Decodificador de 3 entradas a 8 salidas.

2. Multiplexor de 4 canales.

3. Codificador de 4 canales a 2.

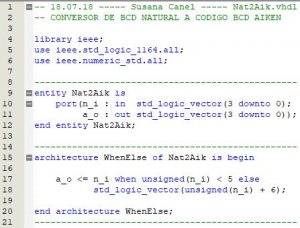

4. Conversor de código BCD natural a BCD Aiken.