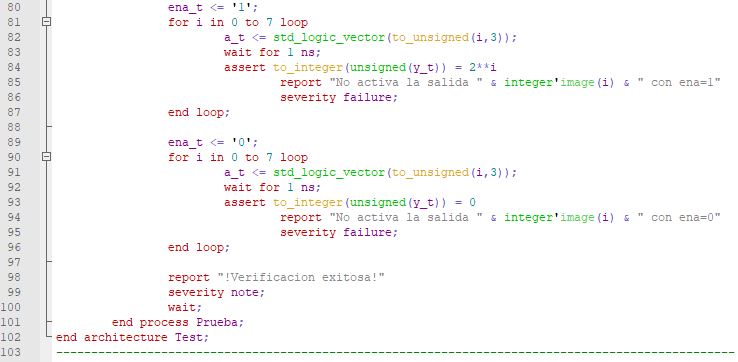

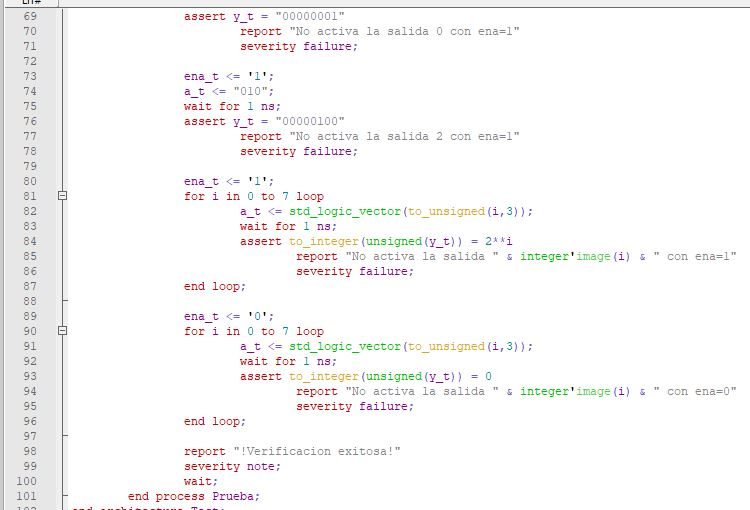

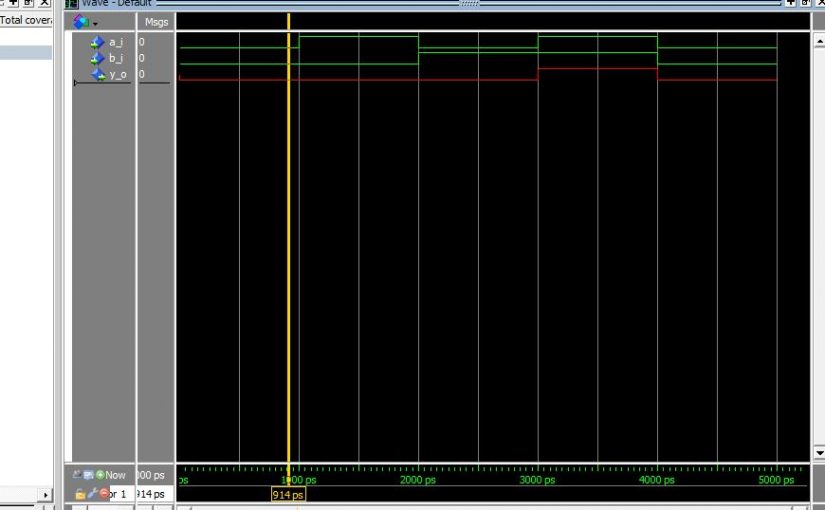

En este video te muestro cómo generar los estímulos y controlar si la salida del decodificador es la esperada usando una sentencia “for”. Vemos que hay que realizar adaptaciones al testbench anterior cuando usamos la sentencia for, incluir el package numeric_std y usar un atributo ‘image. En la simulación comparo con las formas de ondas generadas en el testbench anterior y veo las limitaciones que se obtienen en la simulación cuando usamos la sentencia “for” para generar las señales.

Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.