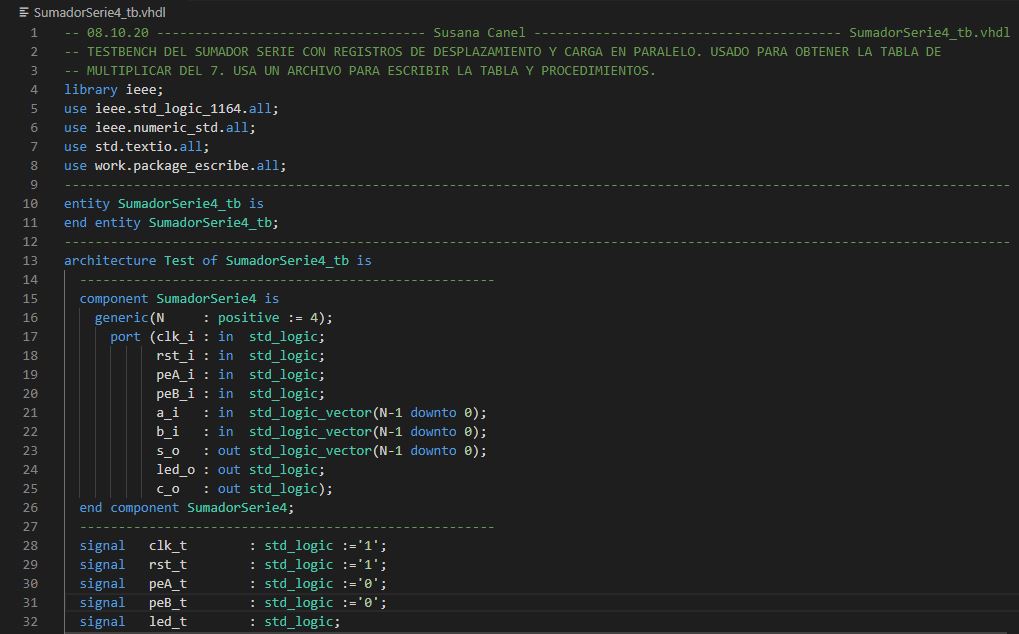

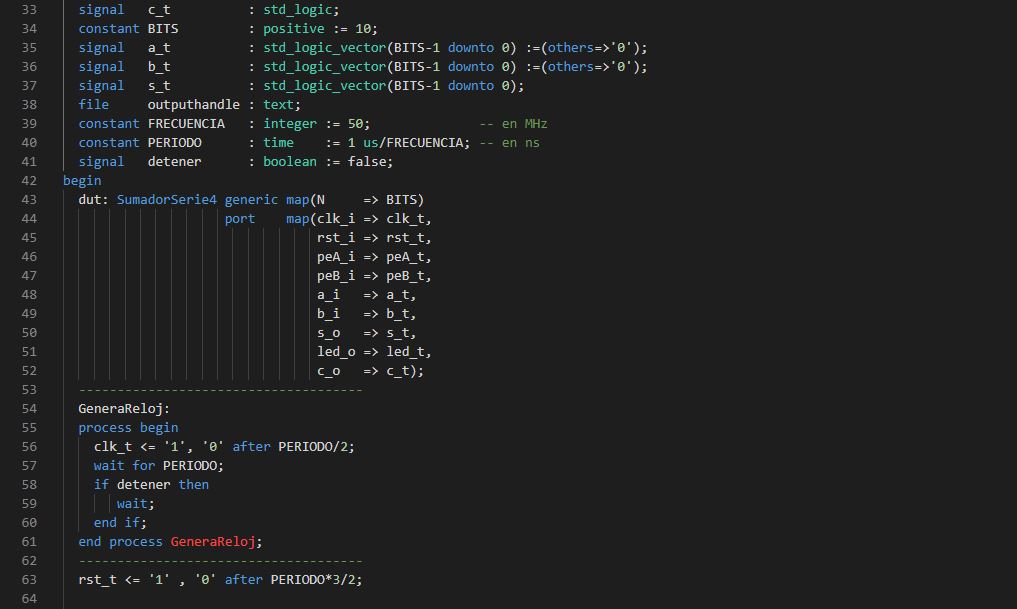

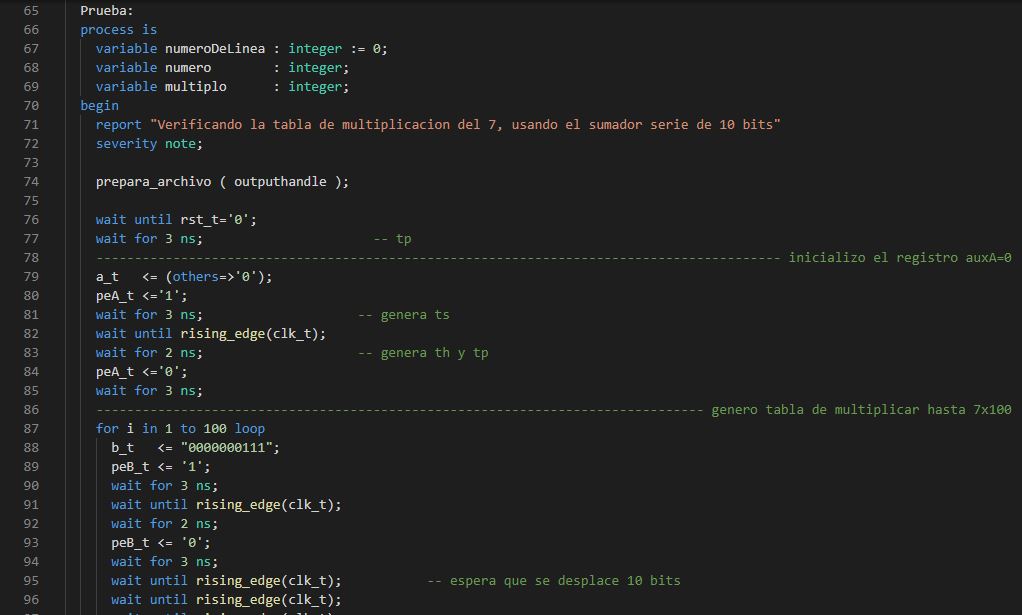

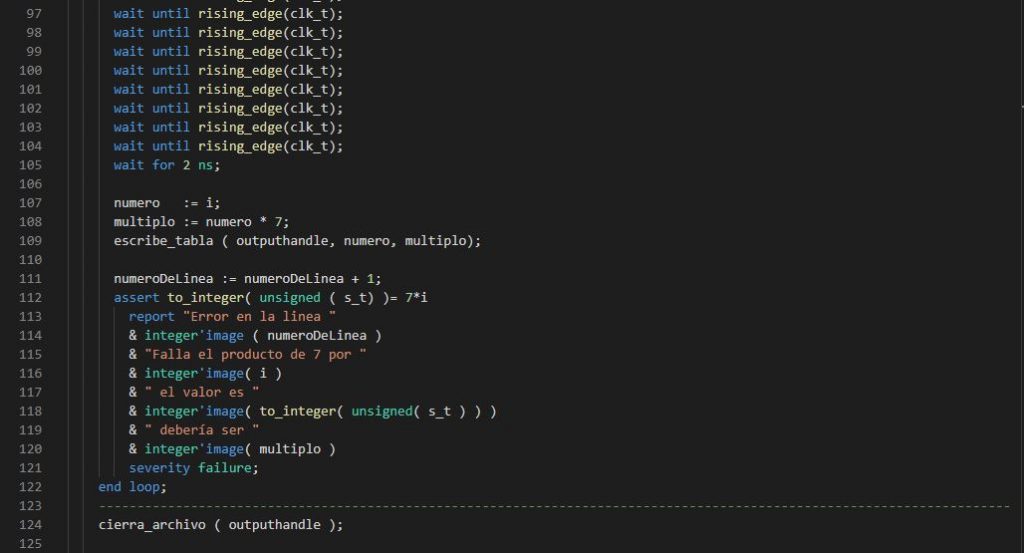

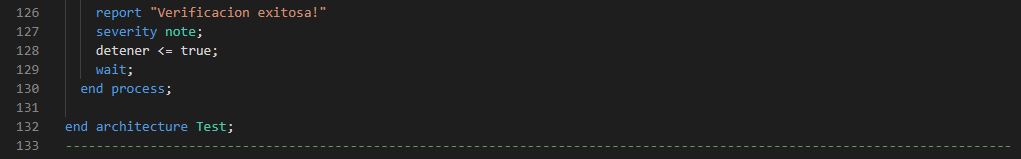

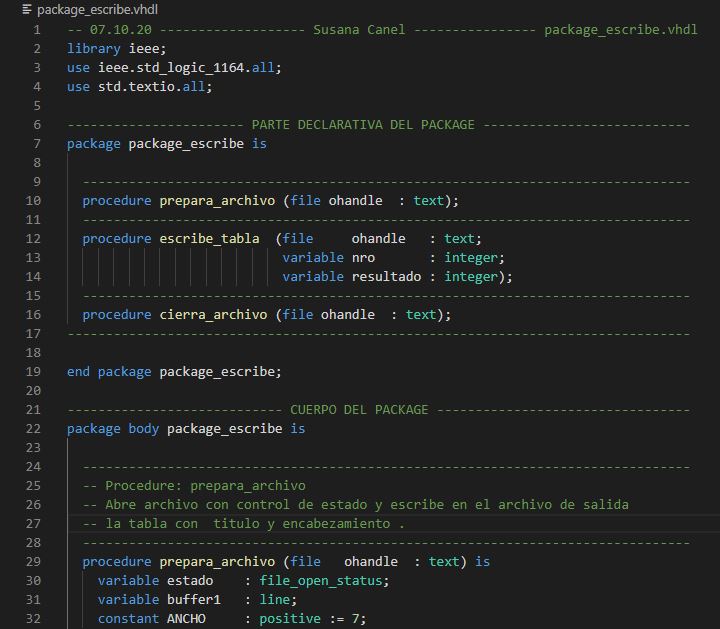

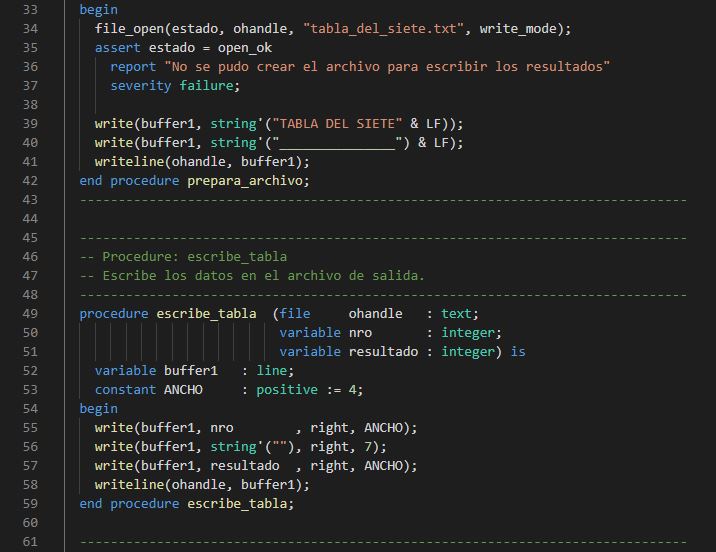

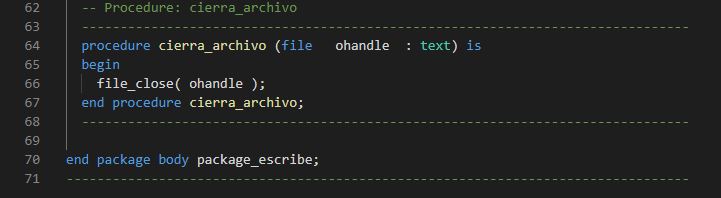

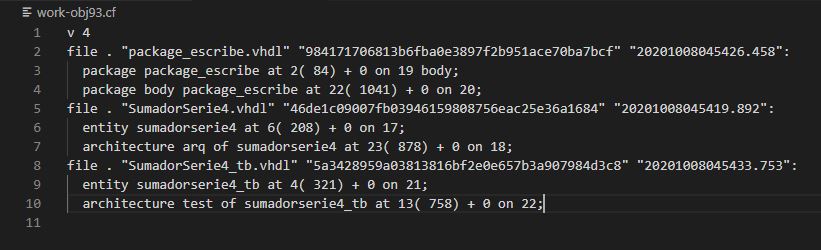

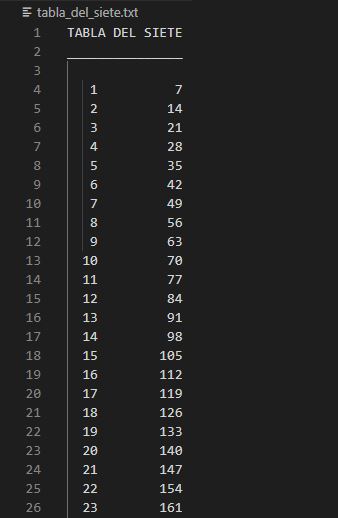

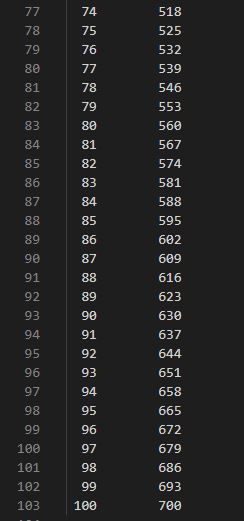

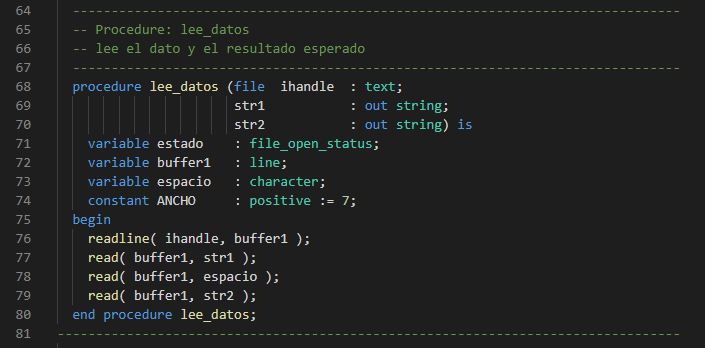

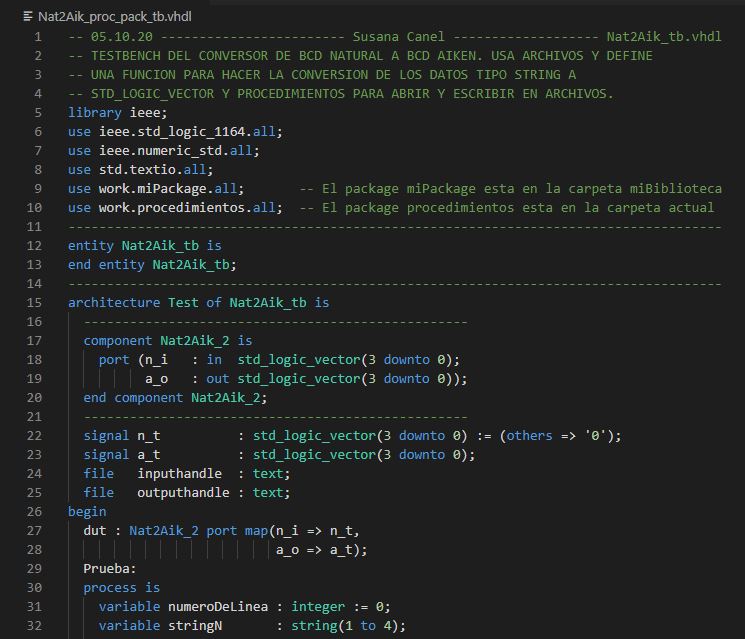

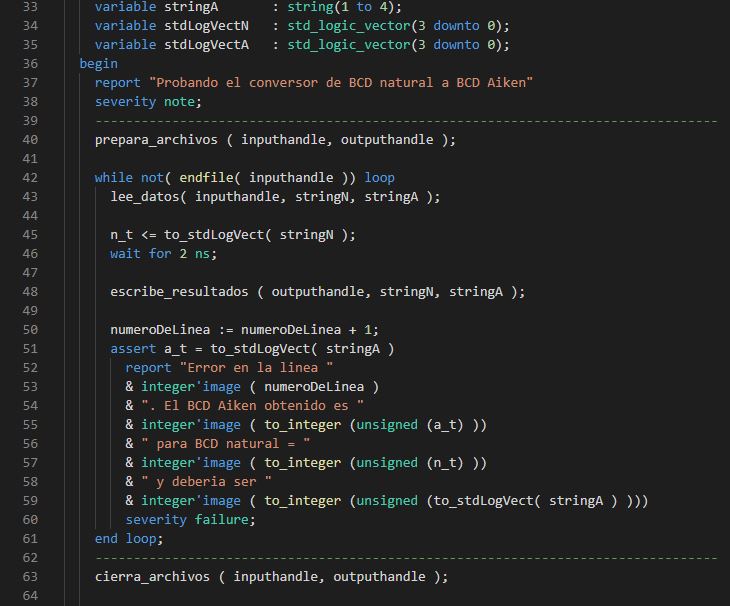

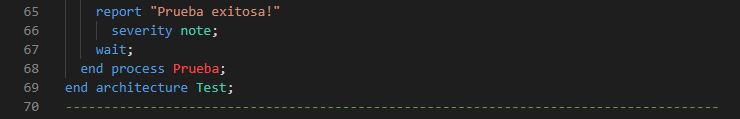

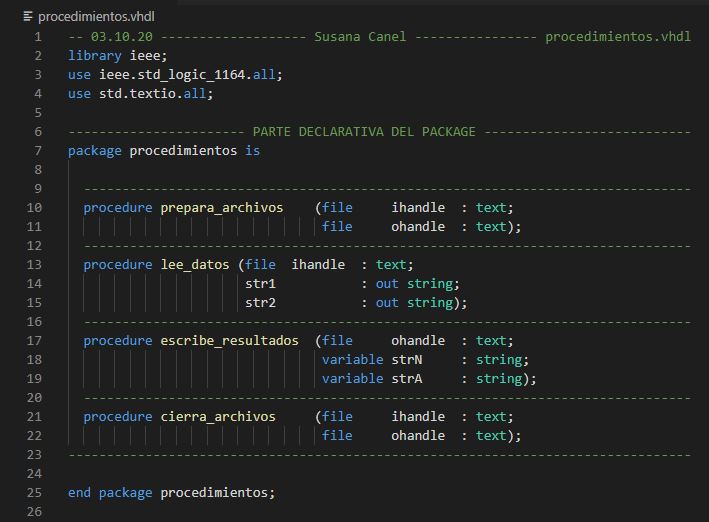

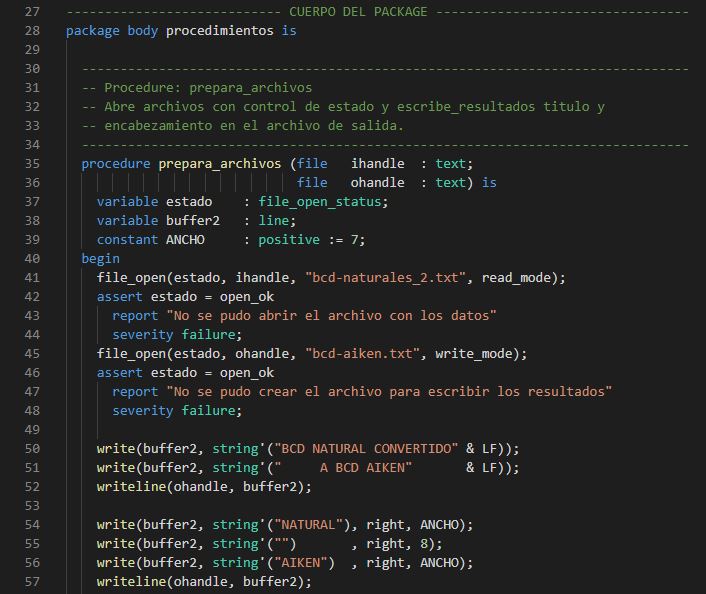

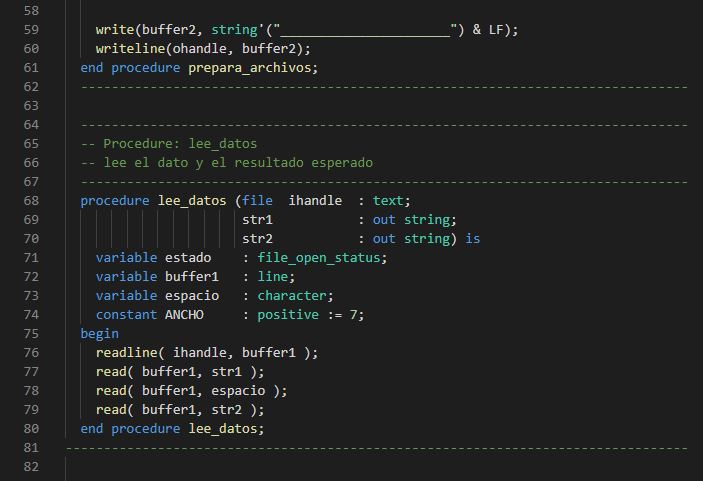

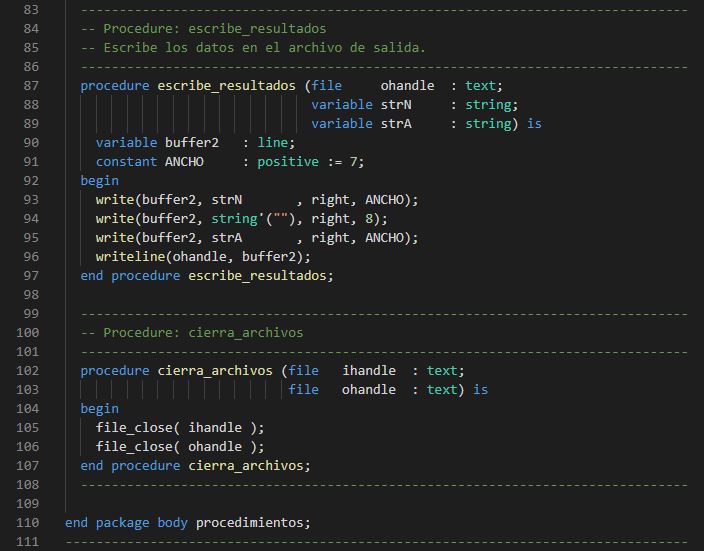

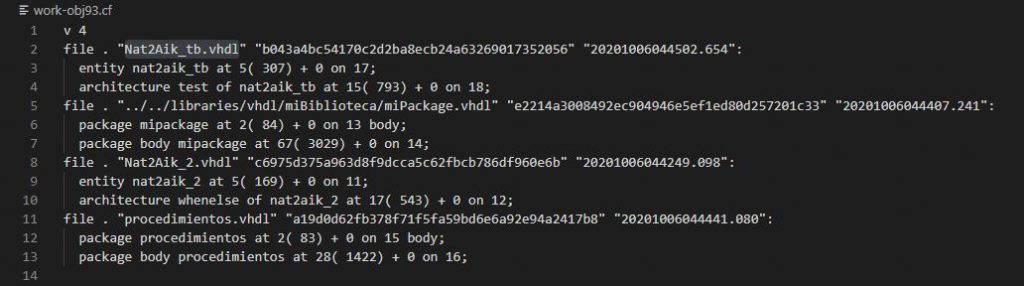

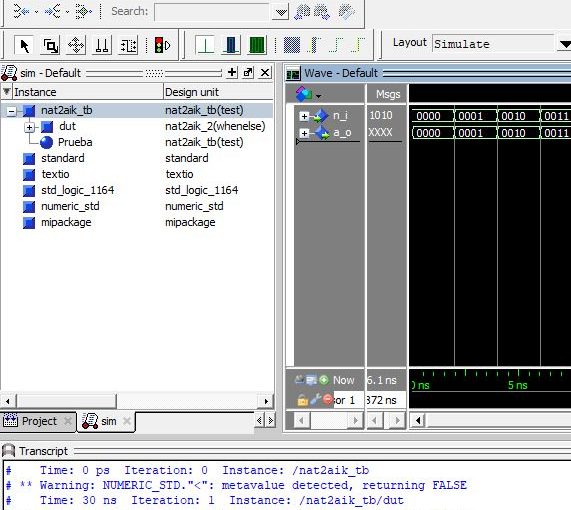

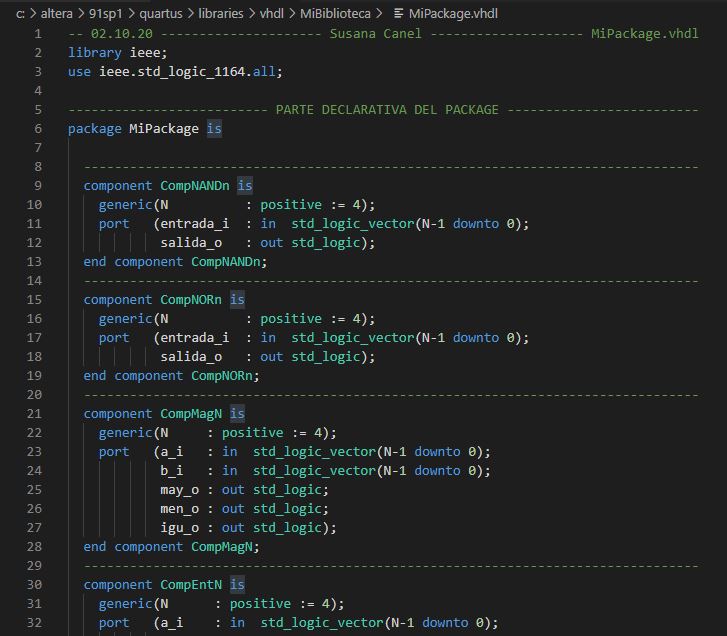

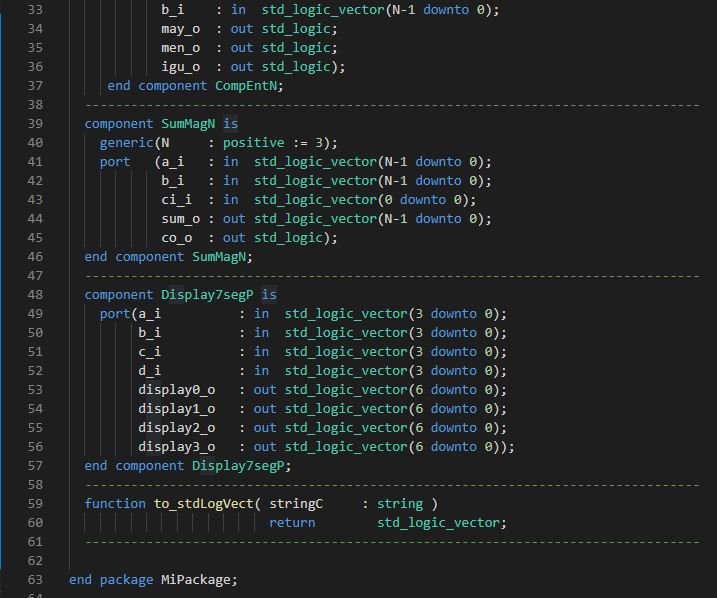

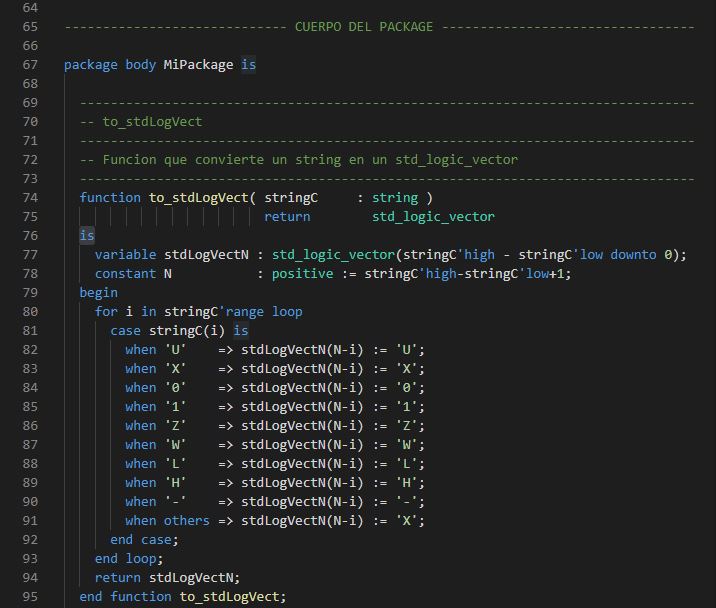

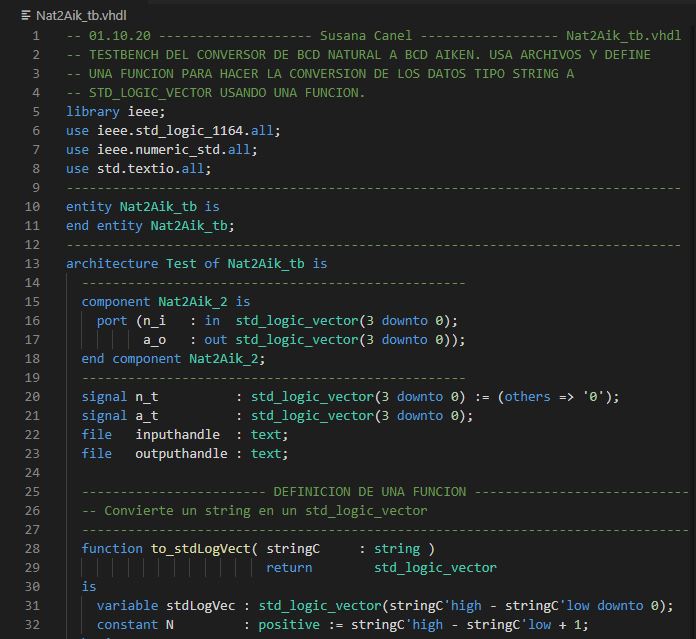

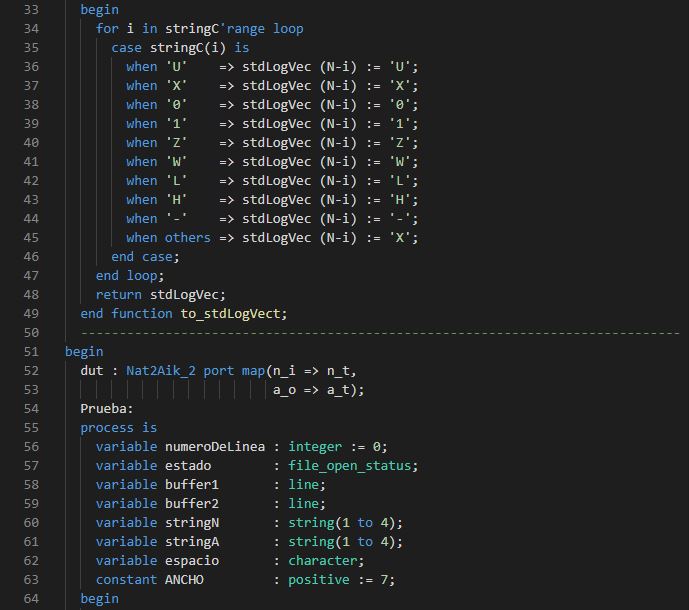

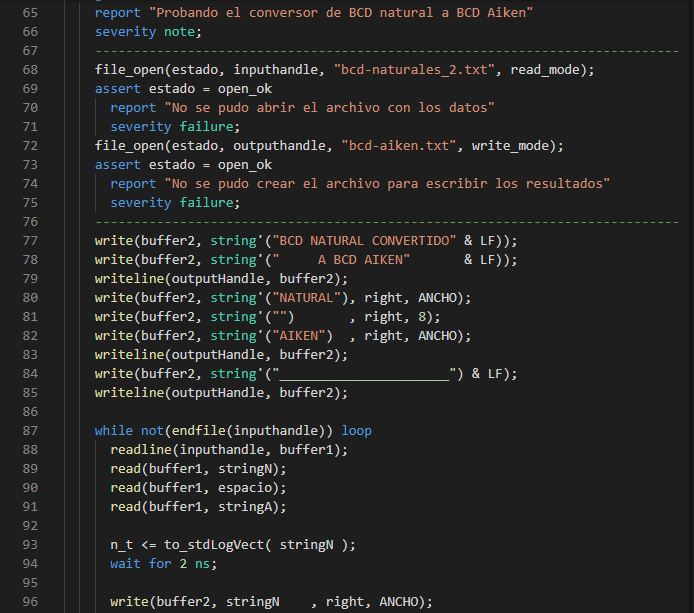

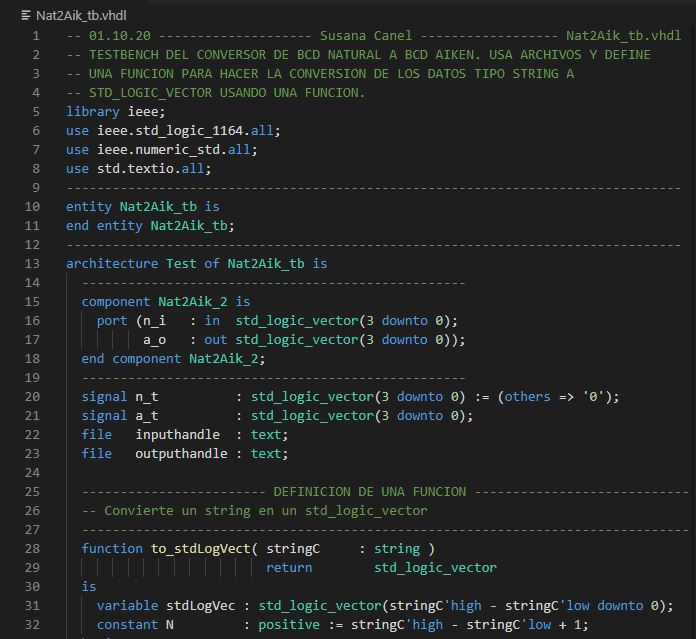

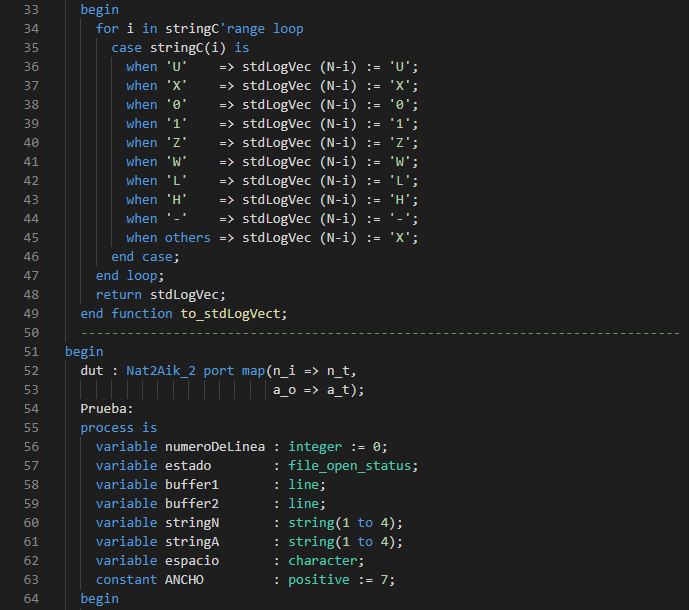

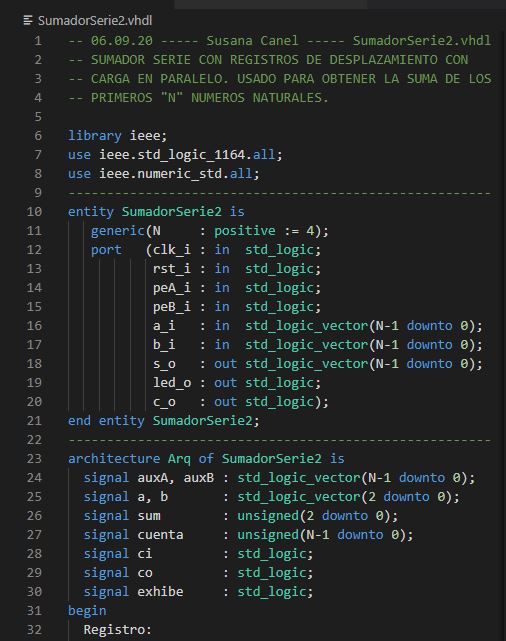

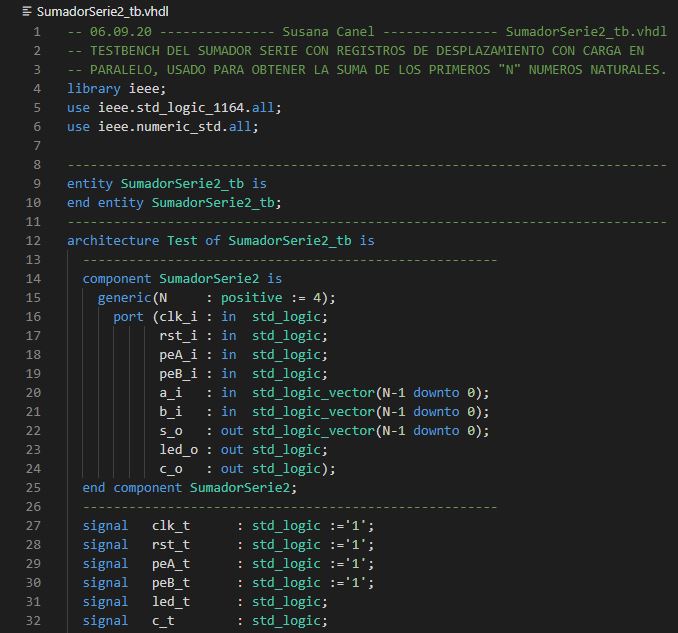

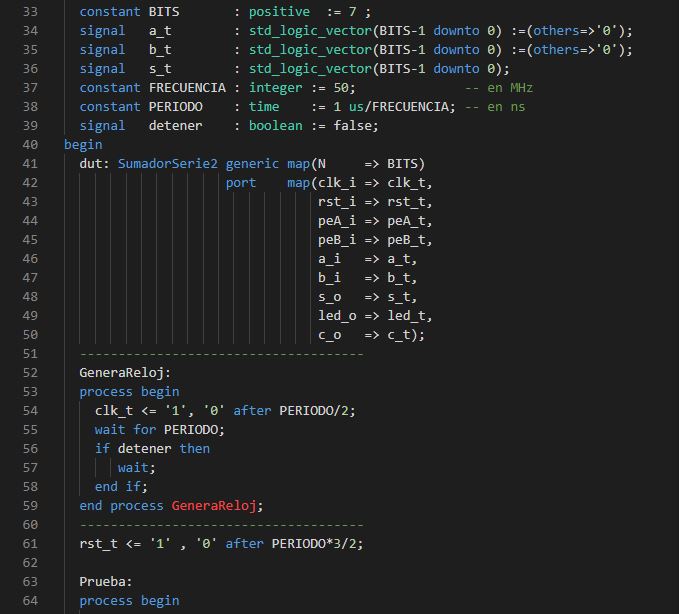

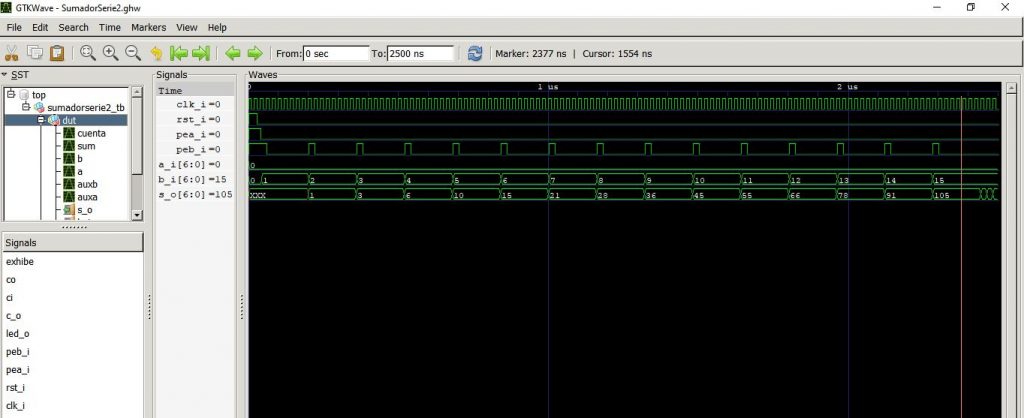

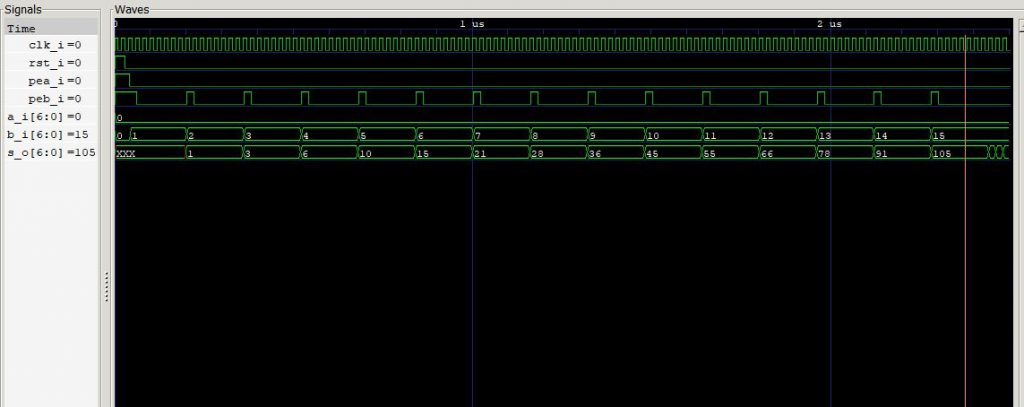

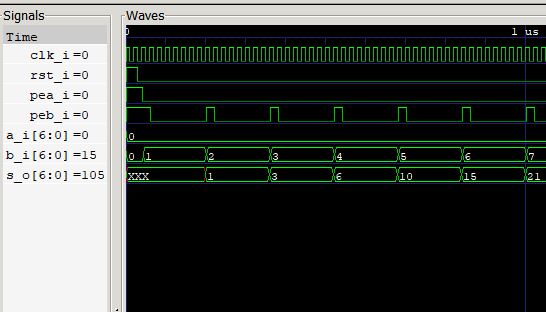

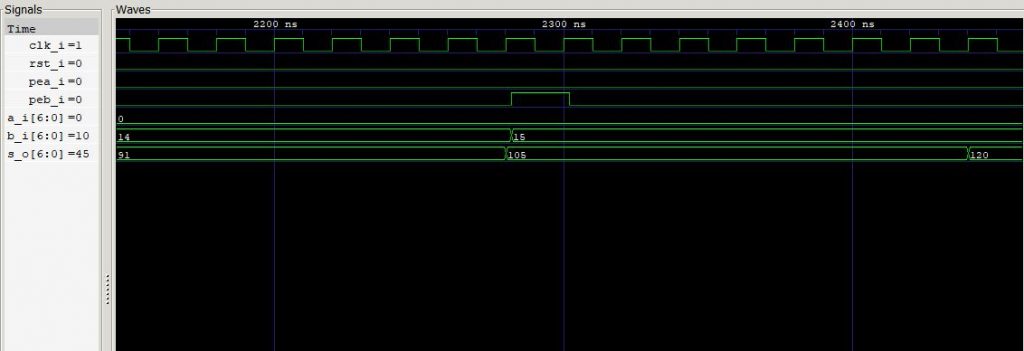

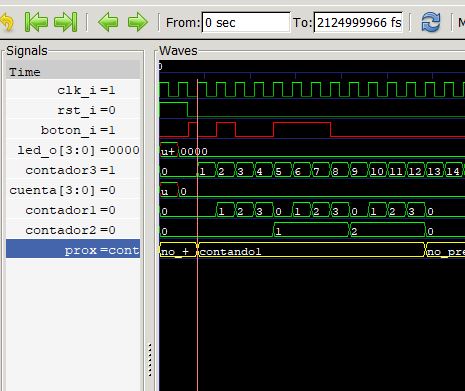

En este video describo un testbench para una nueva aplicación del sumador serie: generar una tabla de multiplicación. Defino un package propio y en él declaro procedimientos para usar un archivo para los resultados. En ese archivo de salida escribo la tabla de multiplicación del 7.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entrá en /contactame/.

Puedes ver y descargar mis códigos fuente de: https://github.com/susanacanel/proyectos-vhdl.