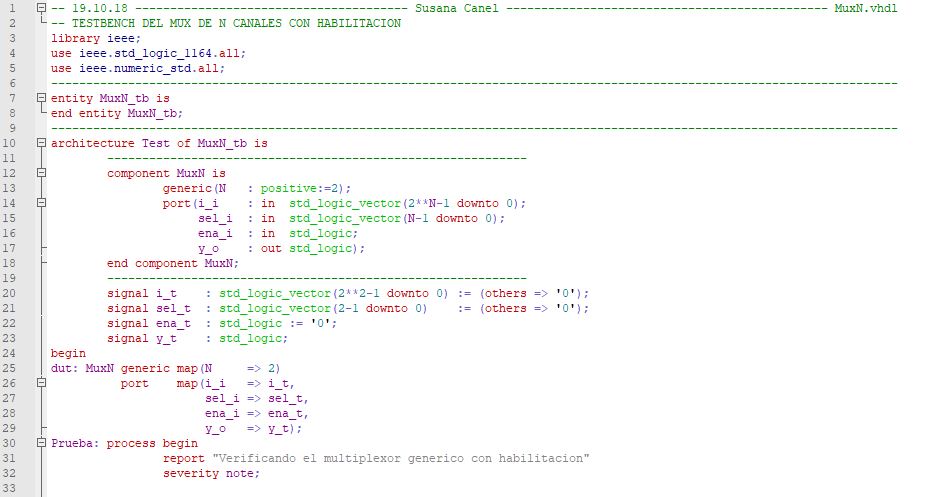

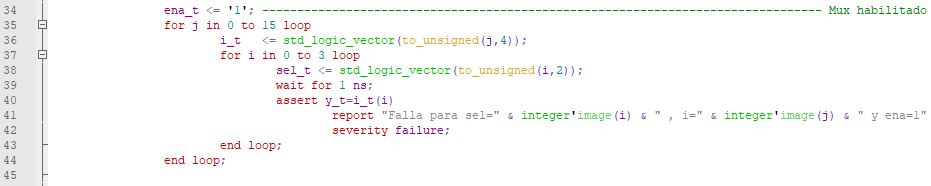

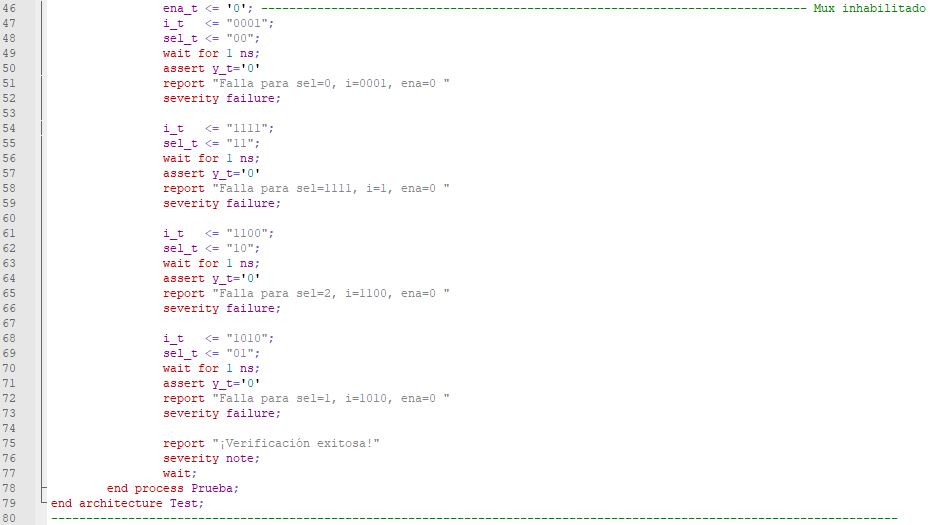

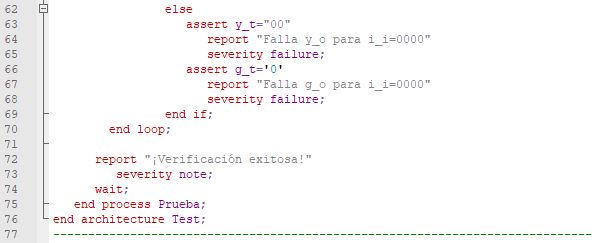

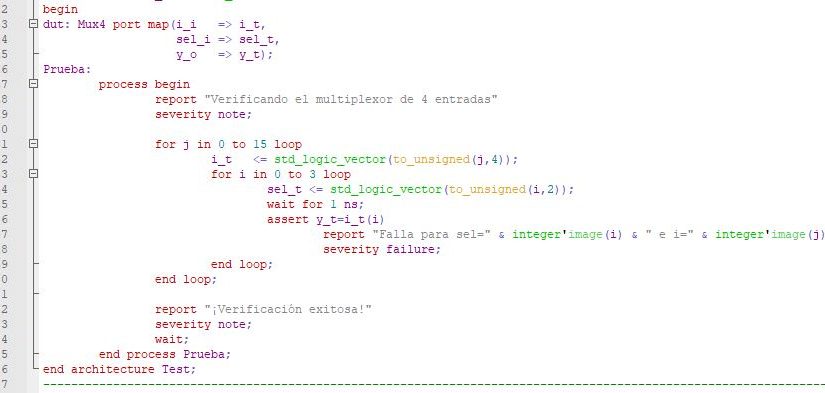

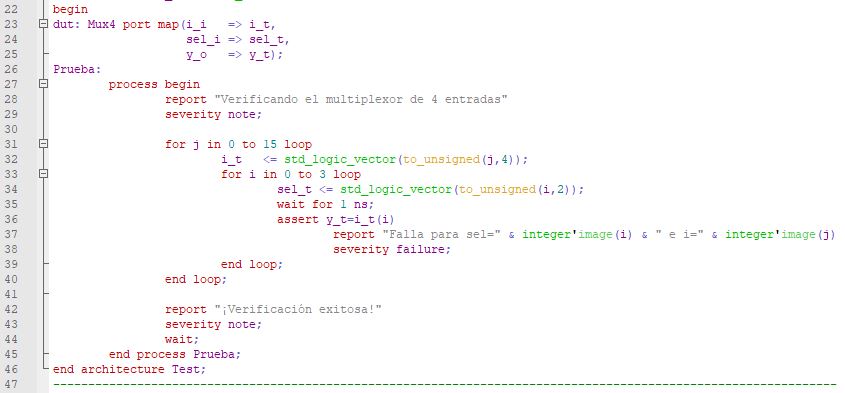

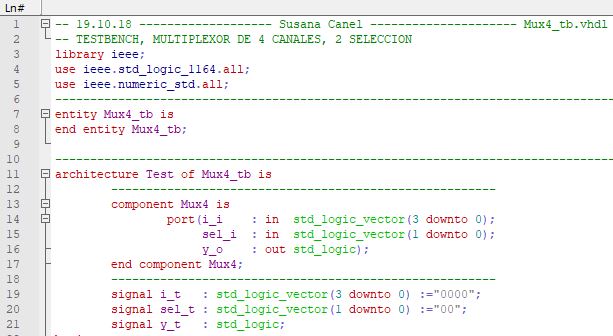

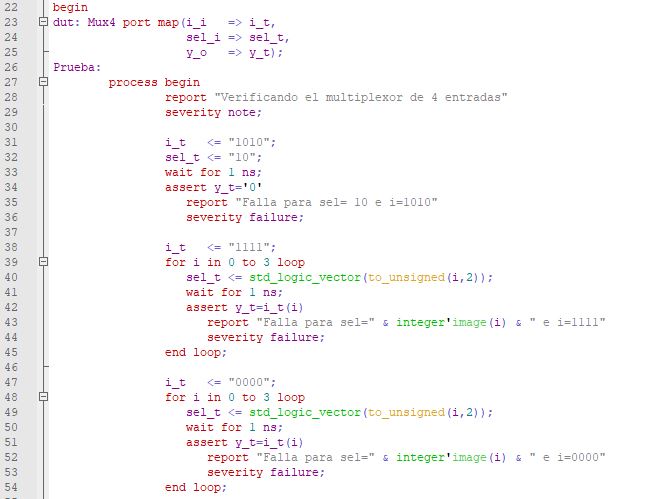

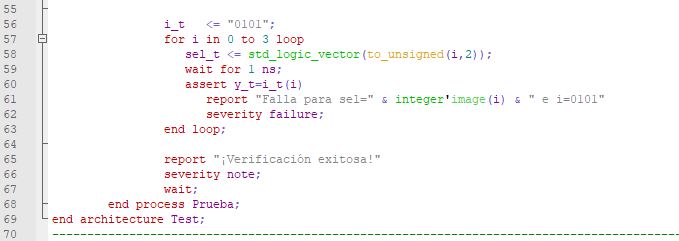

En este video te muestro el testbench de un multiplexor genérico, de N canales, con entrada de habilitación. El testbench se realiza para un caso en particular. Uso “others” para dar el valor inicial a las señales del testbench. Sentencia for…loop. Uso generic map dado que la descripción era genérica. Uso port map. Uso el package numeric_std que necesita la función to_unsigned.

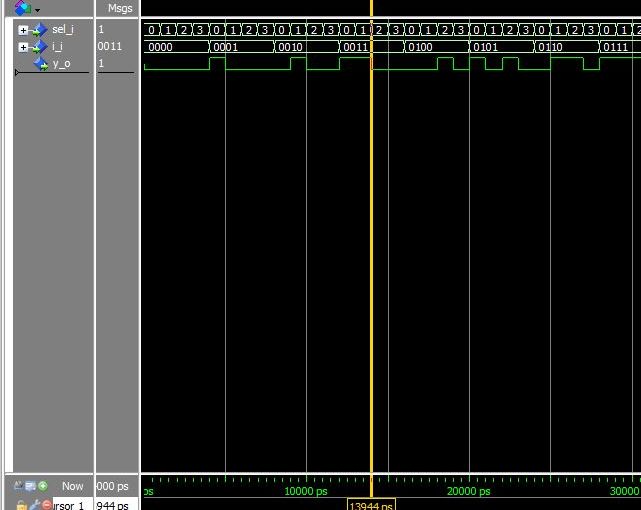

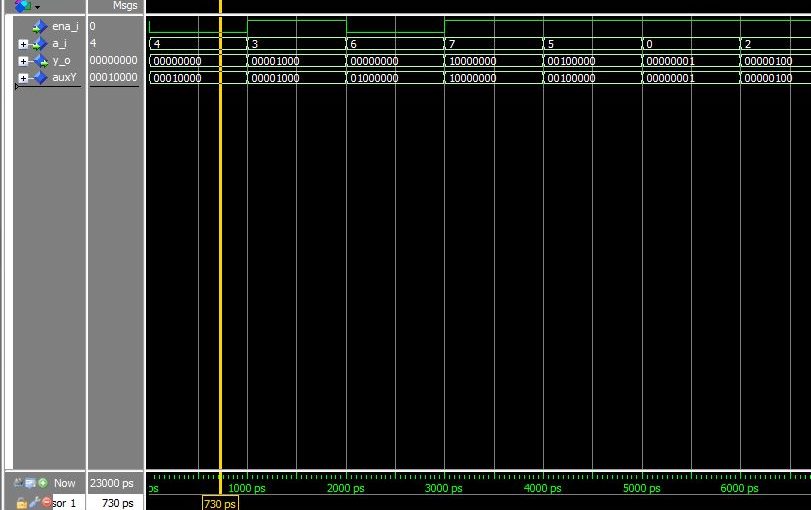

Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.