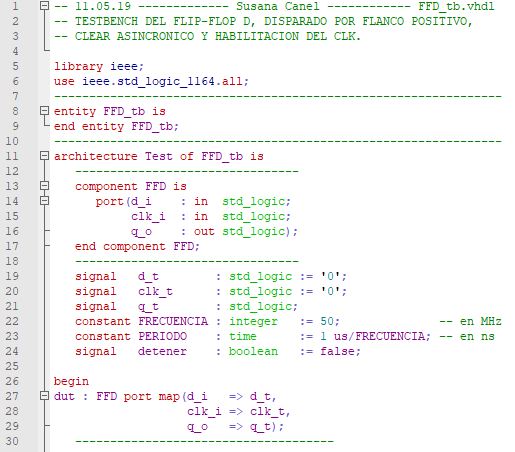

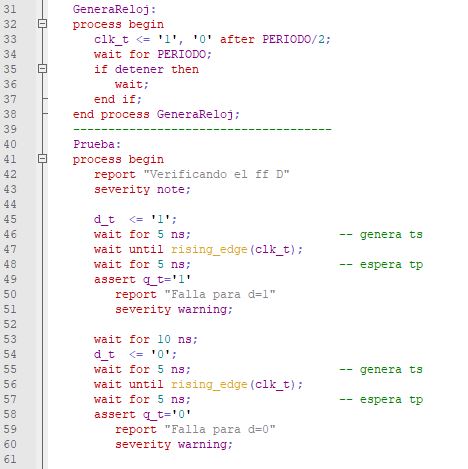

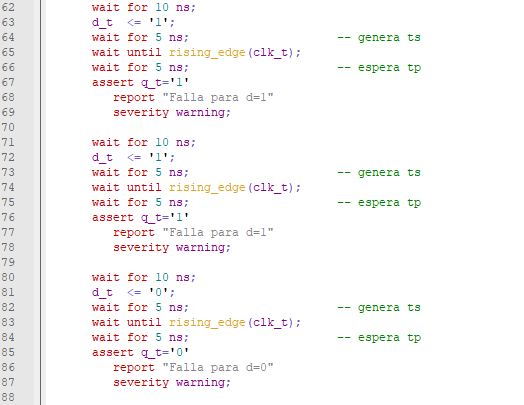

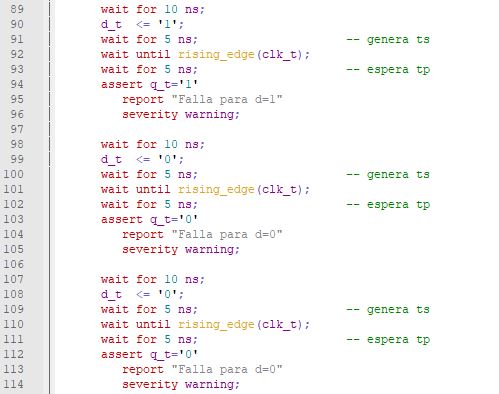

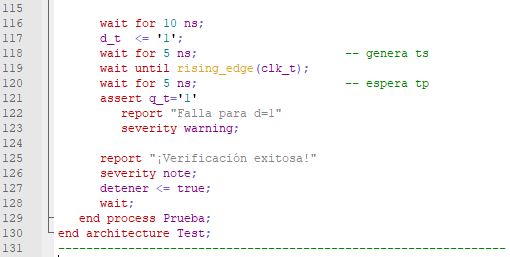

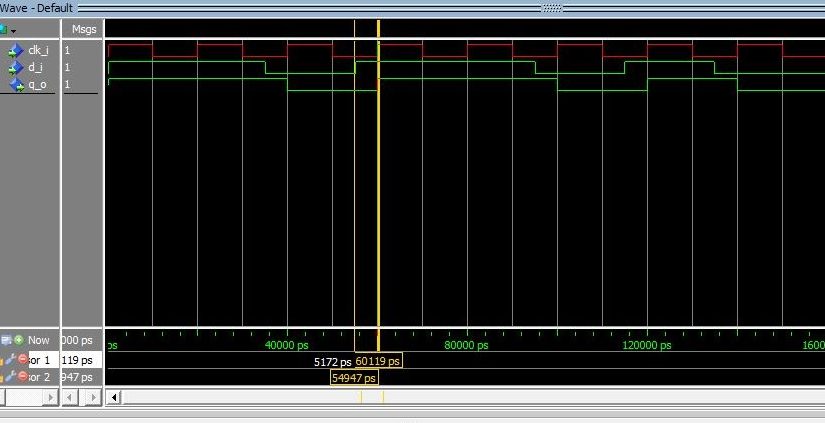

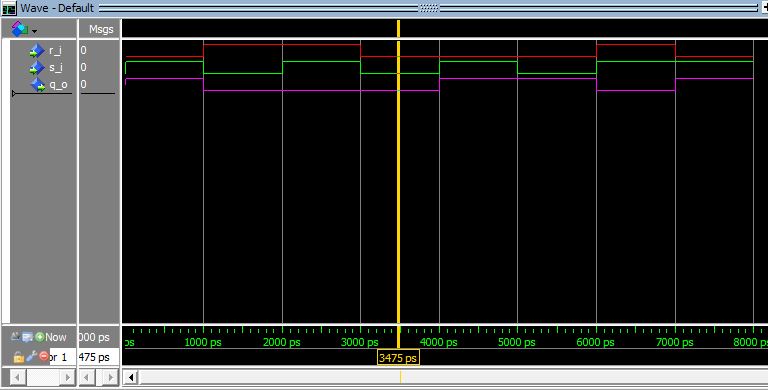

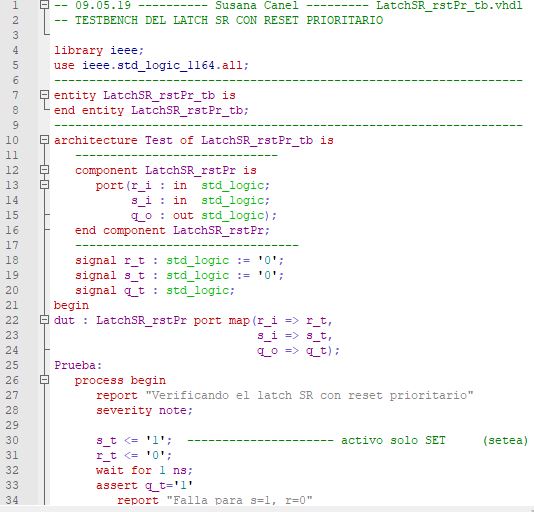

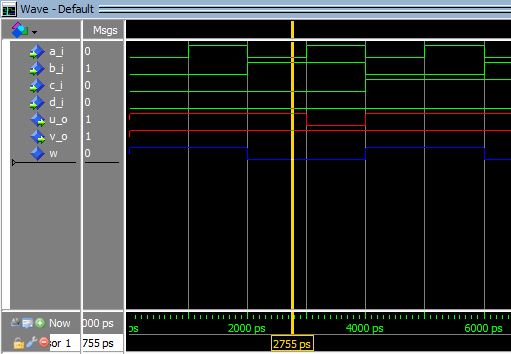

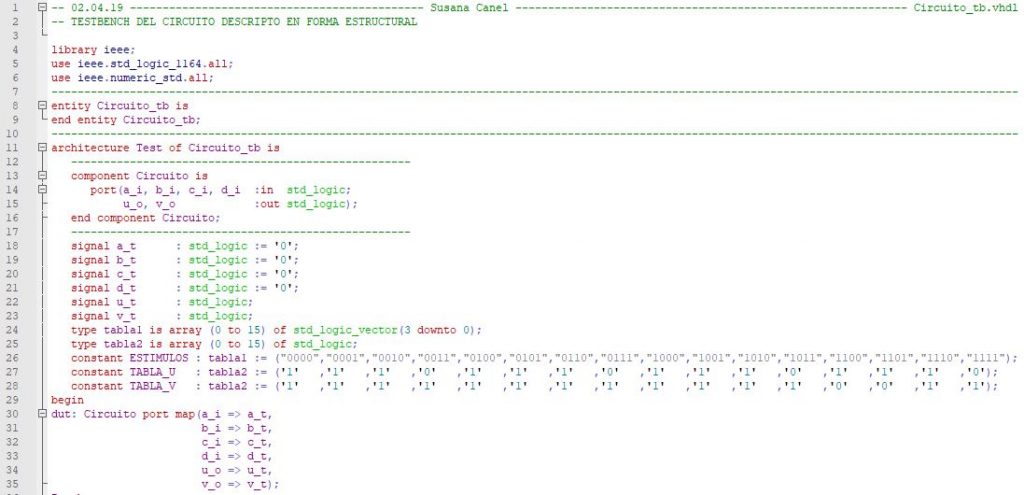

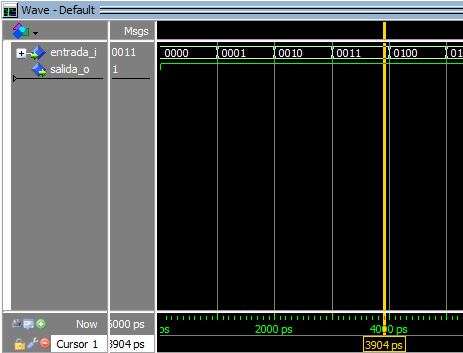

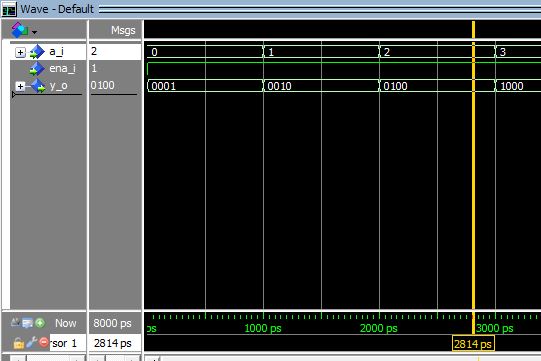

En este testbench del flip-flop D modelizo el tiempo para poder generar la señal periodica del reloj. Uso constantes, división entera entre constantes (con truncamiento) para generar el periodo de la señal de reloj. Uso el tipo de datos físico, o sea aquellos que tienen un valor y una unidad, en este caso “time”. Defino una señal de tipo “booleano” para detener un proceso. Uso dos procesos, recuerdo que se ejecutan en modo concurrente. Modelizo el tiempo de establecimiento, el tiempo de mantenimiento y genero el ancho de los pulsos. Genero una señal pulsante infinita. Simulo con el ModelSim para verificar el correcto funcionamiento de la descripción y también la generación de la señal del reloj y los distintos tiempos modelizados. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/ .