Curso de VHDL (blog)

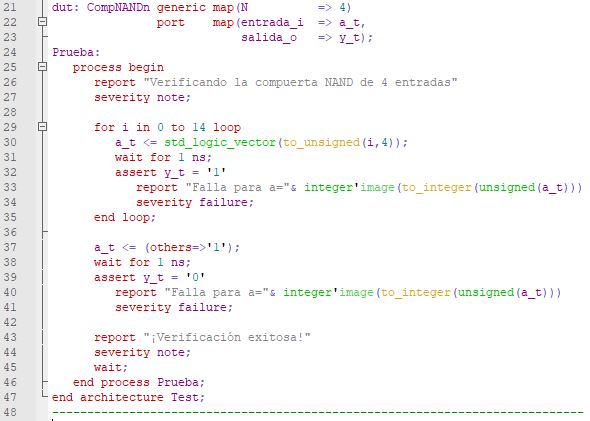

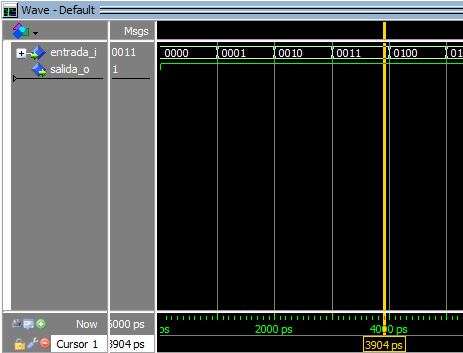

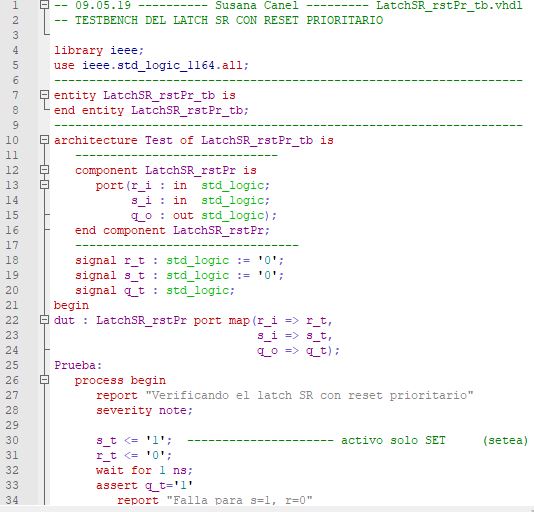

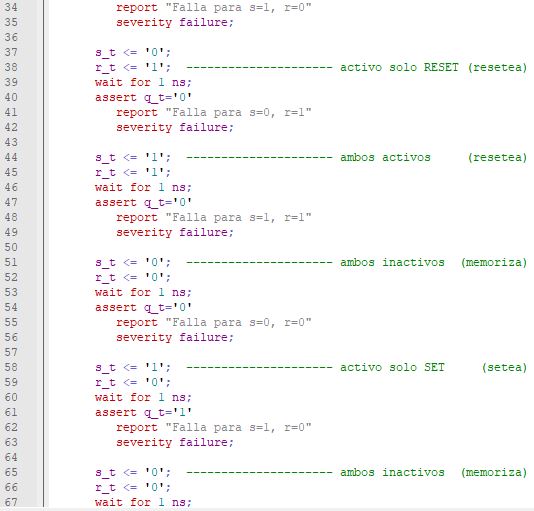

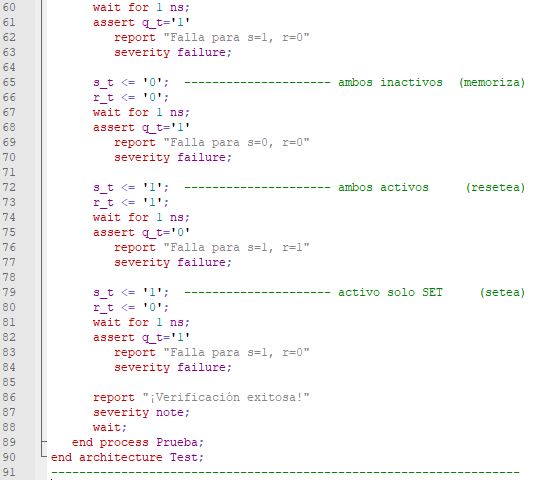

Lección 9.V49. Testbench y simulación de un latch SR con reset prioritario.

En este video te muestro el testbench para el latch SR con reset prioritario. Luego lo uso para verificar el correcto funcionamiento realizando la simulación a través del ModelSim. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/

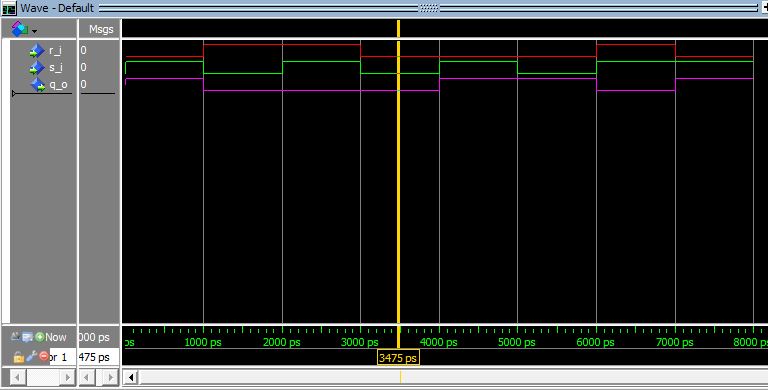

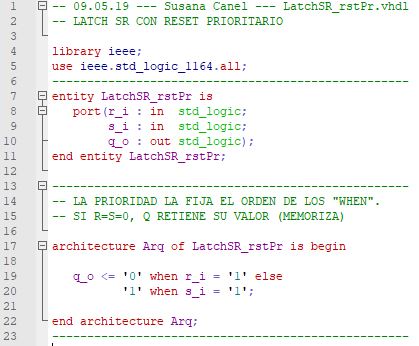

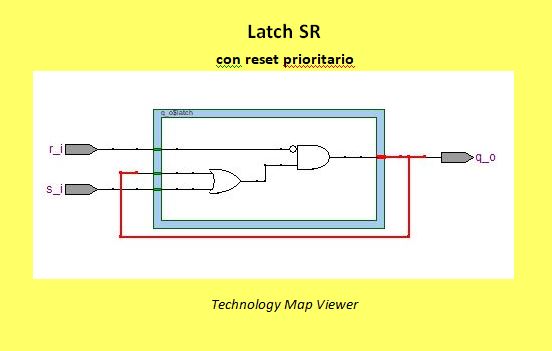

Lección 9.V48. Descripción de un latch SR con reset prioritario.

En este video te muestro la descripción de un latch SR con reset prioritario. Uso la sentencia condicionada “when…else” para generar la prioridad y al usarla incompletamente especificada infiero memoria. Compilo. Analizo los “warnings” y te muestro el esquemático generado con la herramienta “Technology Map Viewer” del “Tool” del Quartus II. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/

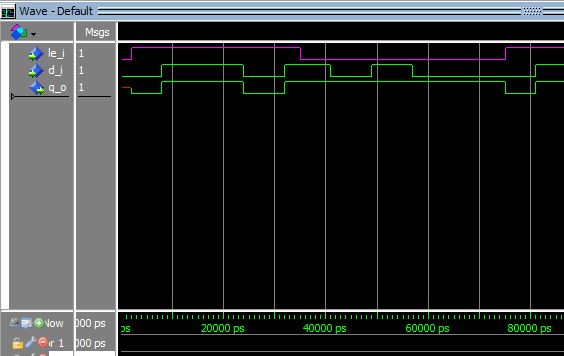

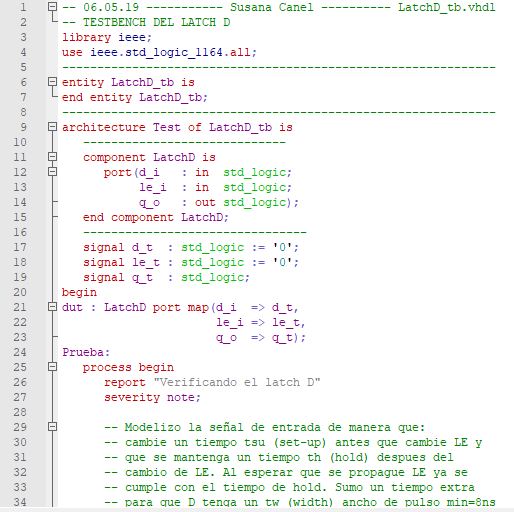

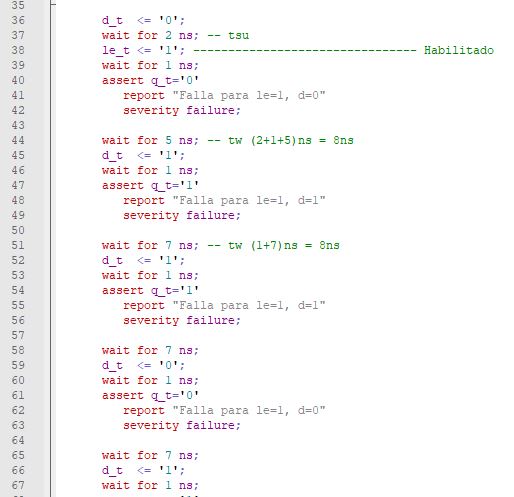

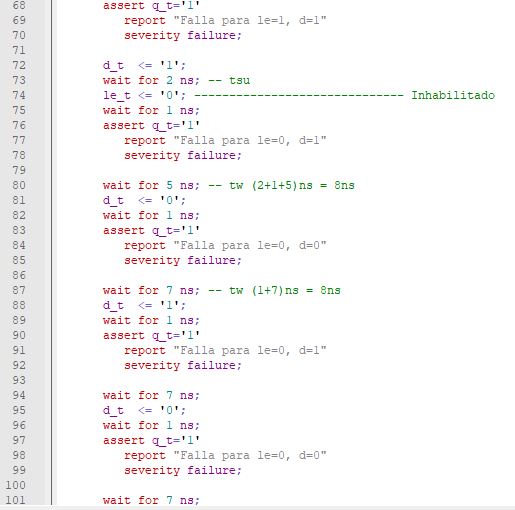

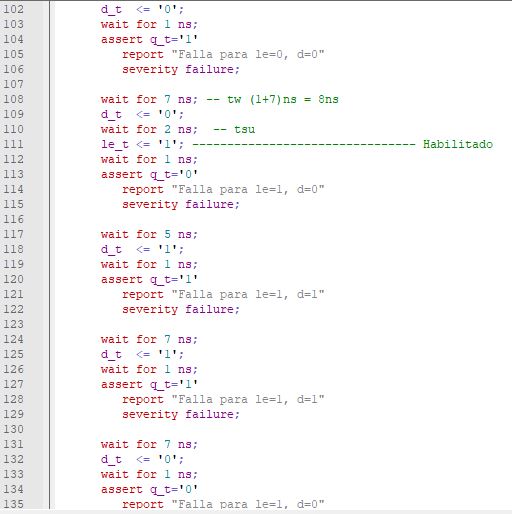

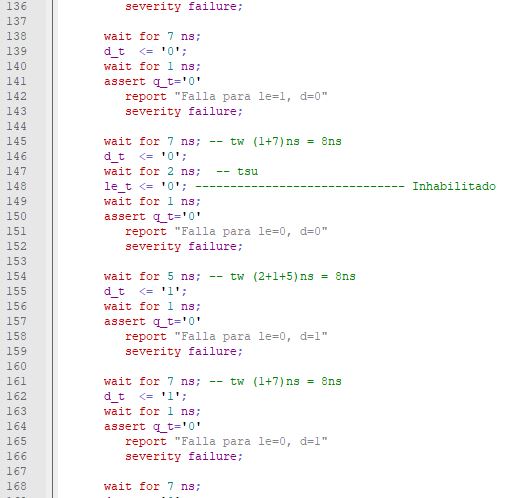

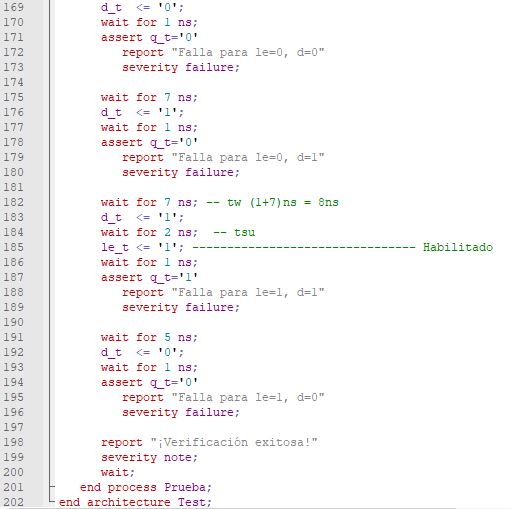

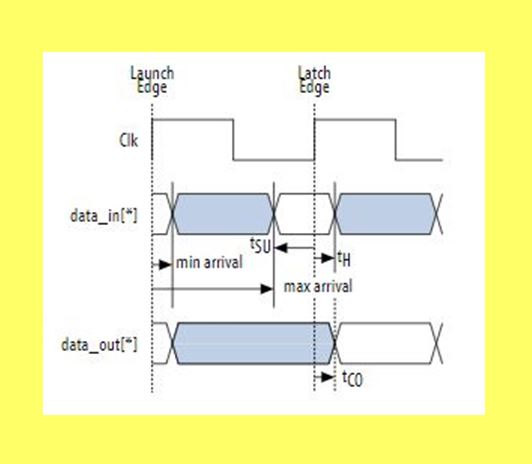

Lección 9.V47. Testbench y simulación del latch D.

En este video te muestro el testbench para el latch D. Modelizo los tiempos a fin de dibujar las señales en el simulador respetando el tiempo de establecimiento (set up), el tiempo de mantenimiento (hold) y el ancho del pulso (width). Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/

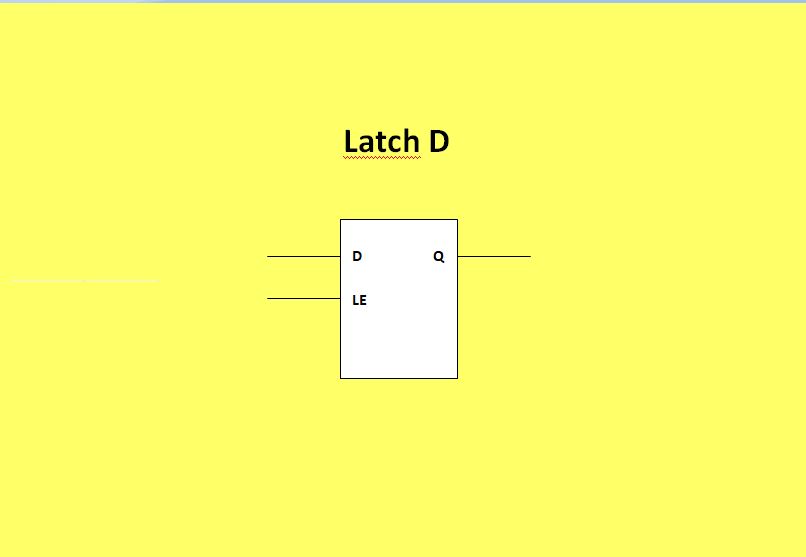

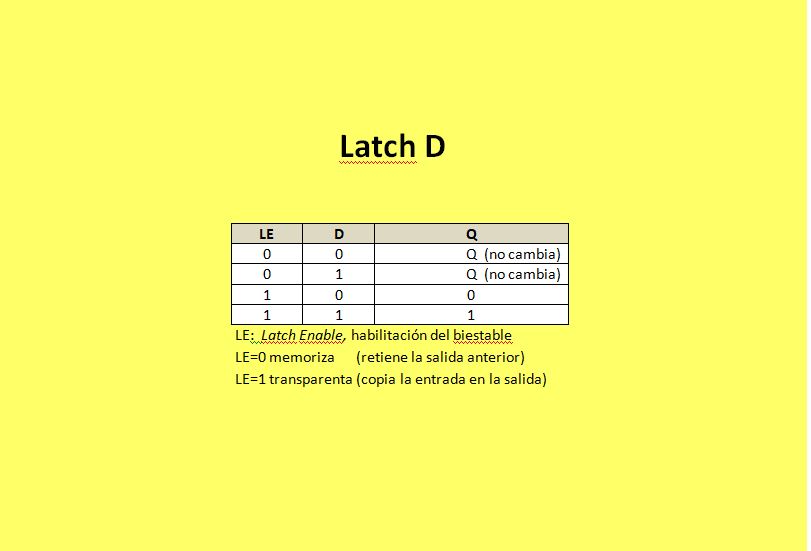

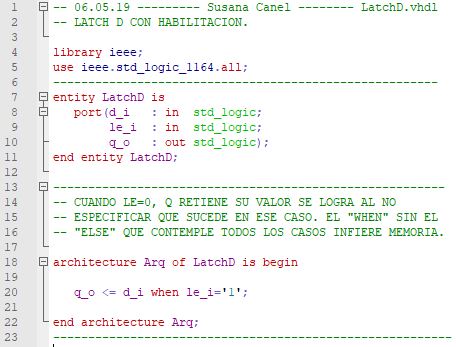

Lección 9.V46. Descripción de un biestable (latch) D.

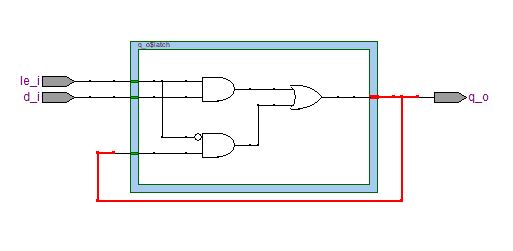

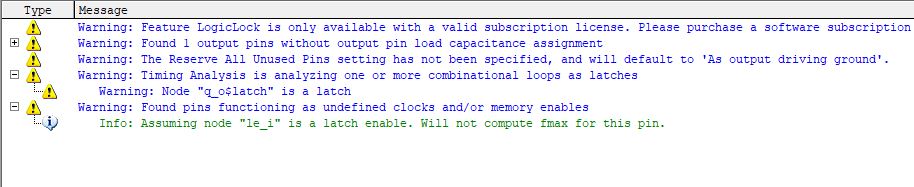

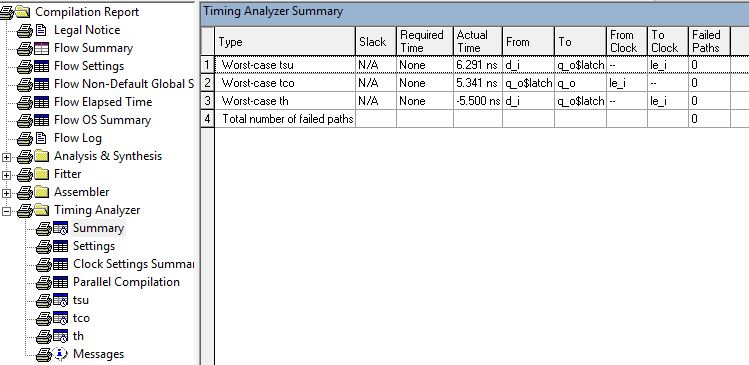

Con este video inicio la segunda parte del curso que consta de las descripciones y los testbenchs de circuitos lógicos secuenciales. Para empezar describo el más sencillos de todos los circuitos que es un biestable (latch) D. Uso la sentencia when…else incompletamente especificada para inferir memoria. Te muestro el esquemático generado por el Technology Map Viewer del Quartus II y te lo explico. Analizo los “warnings” y te muestro y explico los distintos tiempos de propagación del informe producido por la herramienta “timing analyzer”. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar entra en /contactame/.

V45. Cómo sigue el curso.

Comienzo con la parte de circuitos lógicos secuenciales, descripciones, testbenchs y simulaciones.

Esta vez van a ir intercaladas las descripciones y los testbenchs.

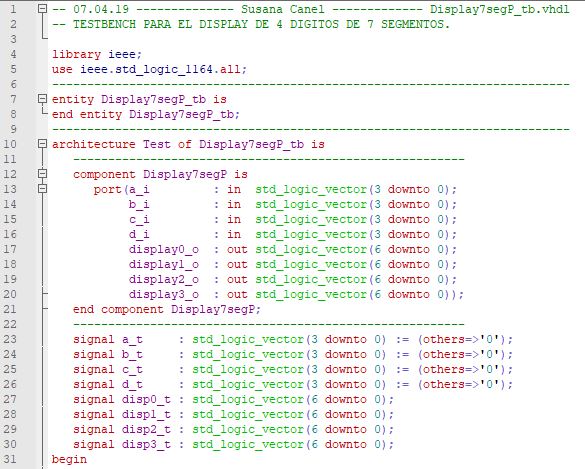

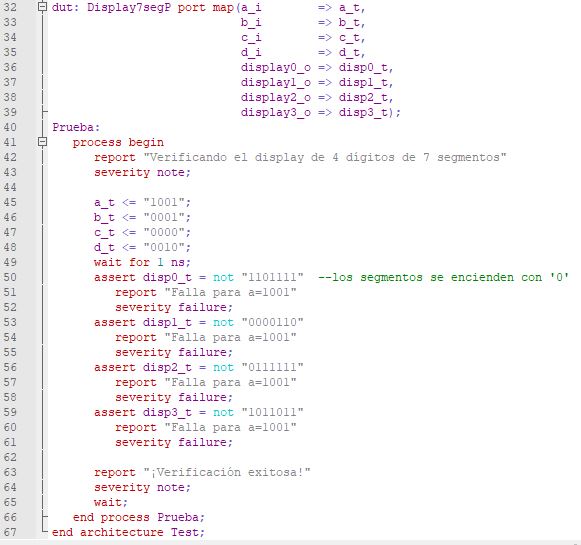

Lección 8.V44. Testbench para 4 dígitos de un display de 7 segmentos.

En este video te muestro el testbench para un display de 4 dígitos de 7 segmentos.

Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.

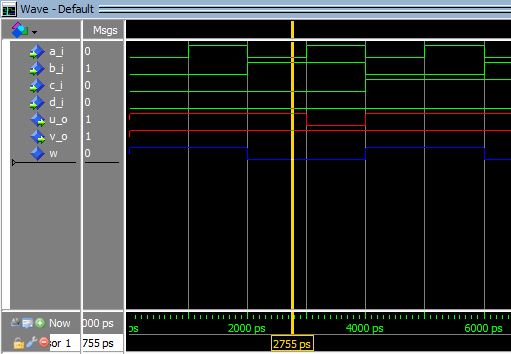

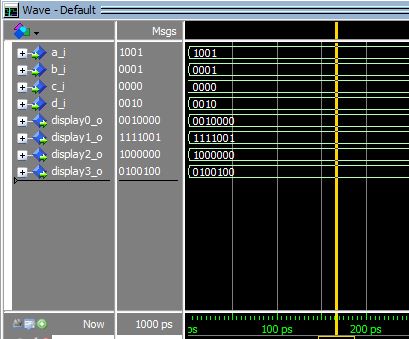

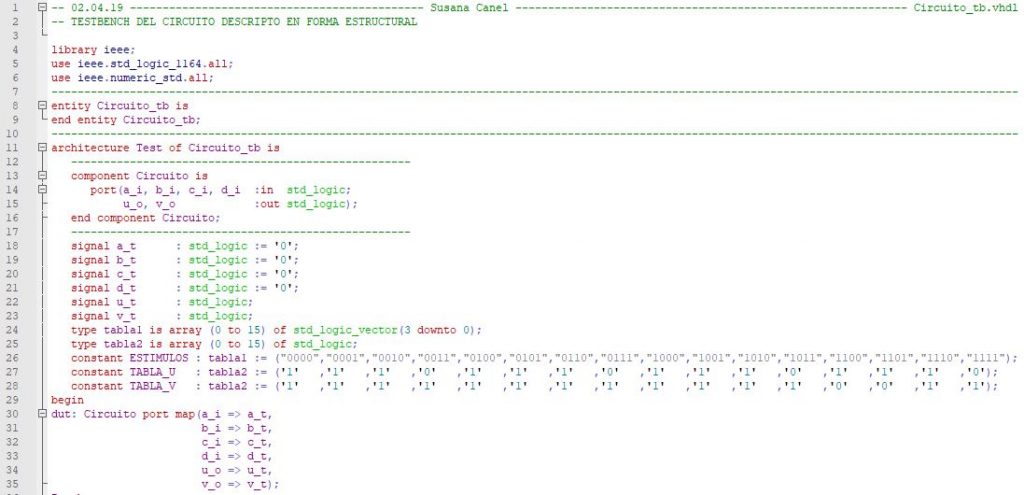

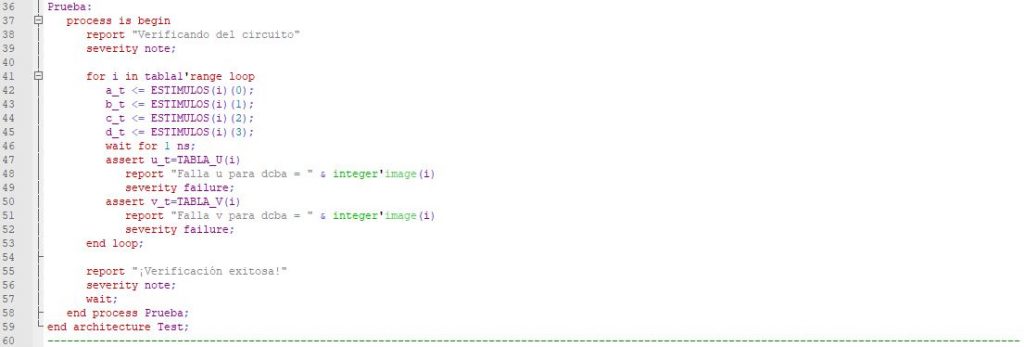

Lección 8.V43. Testbench de un circuito descripto estructuralmente.

En este video te muestro un testbench para el circuito definido en forma estructural. Uso tablas para generar los estímulos de las entradas (type … array). Uso dos subíndices para acceder a un dato de la tabla y a un determinado bit del dato. Con un simple for…loop verifico los 16 casos. Uso los atributos ‘range e ‘image. Incluyo el package numeric_std para poder usar la función: to_integer.

Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.

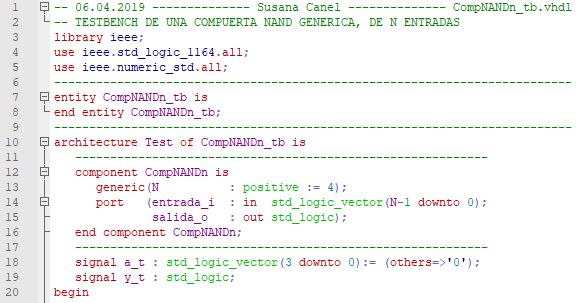

Lección 8.V42. Testbench para una compuerta NAND genérica. For…loop.

En este video te muestro el testbench para una compuerta NAND genérica. Lo resuelvo mediante un for…loop para todos los casos excepto uno. Con el índice del for genero los estímulos para la entrada. Uso el package numeric_std para la función to_integer, y unsigned. Uso el atributo ‘image. Para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.