En este video te muestro cómo falla la simulación en el ModelSim debido a un mal diseño del testbench del contador de módulo 10 que habíamos visto. El error es debido a la forma de generar los pulsos del reset (distinta a la que expliqué en el video anterior). El simulador del ModelSim se “cuelga” y no da ningún informe.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entrá en /contactame/.

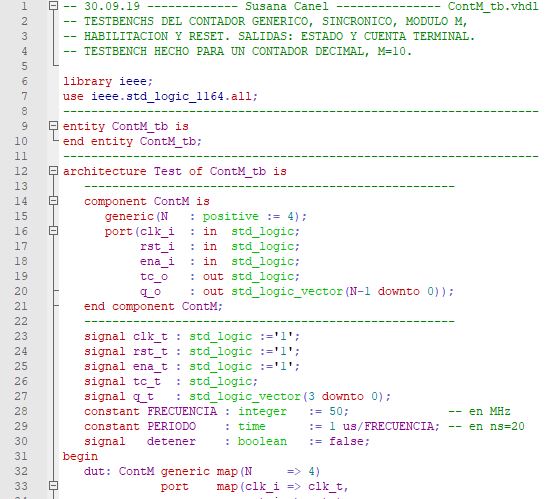

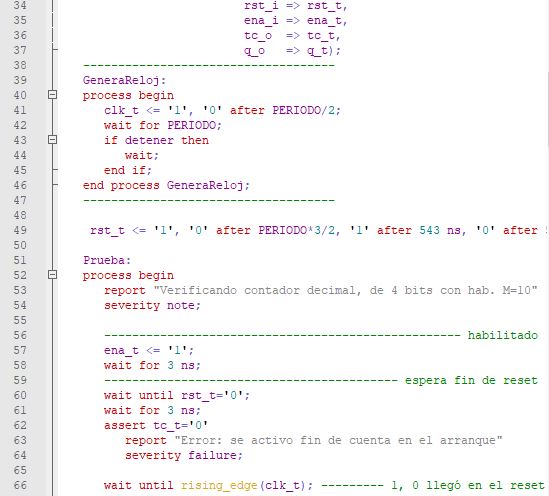

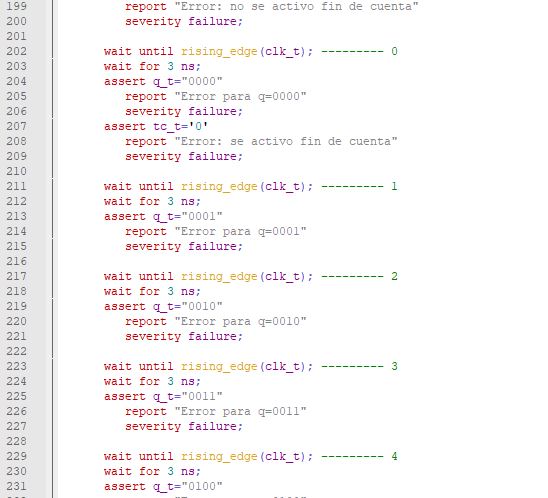

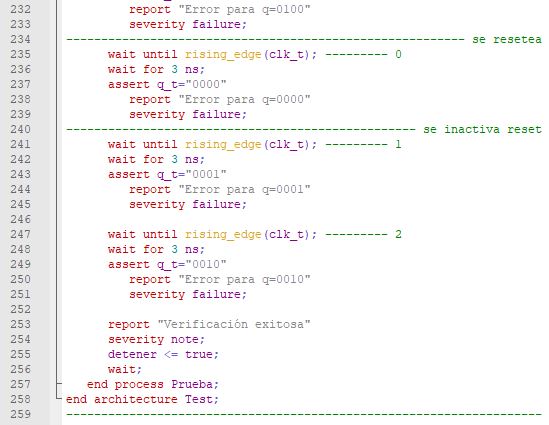

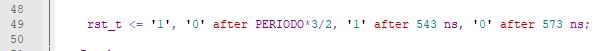

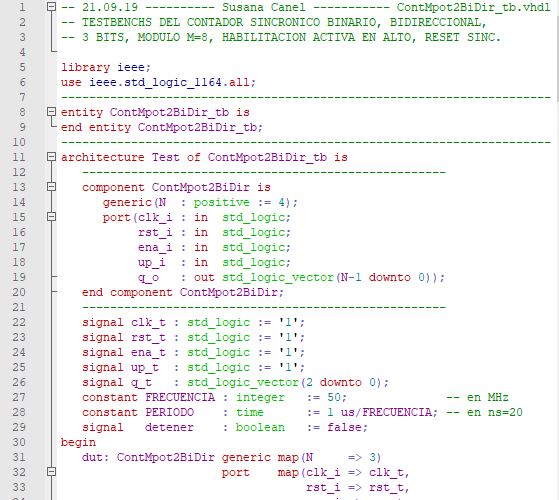

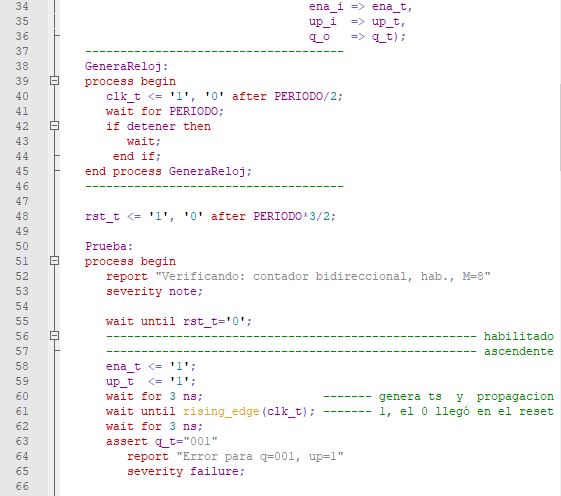

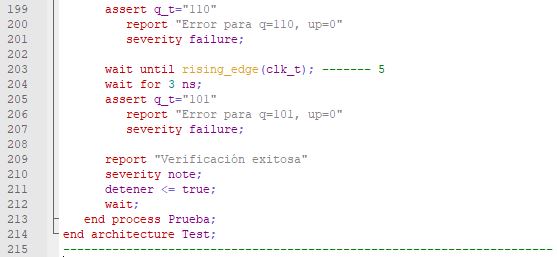

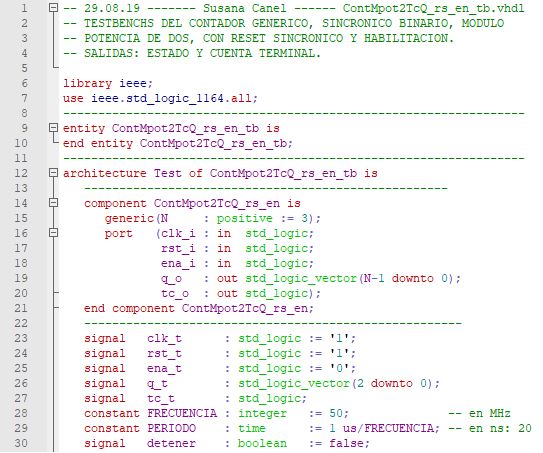

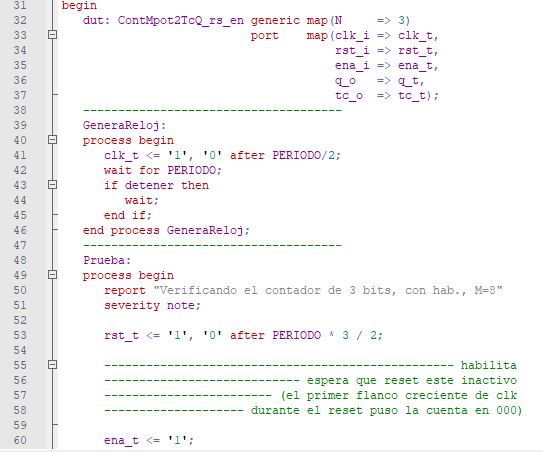

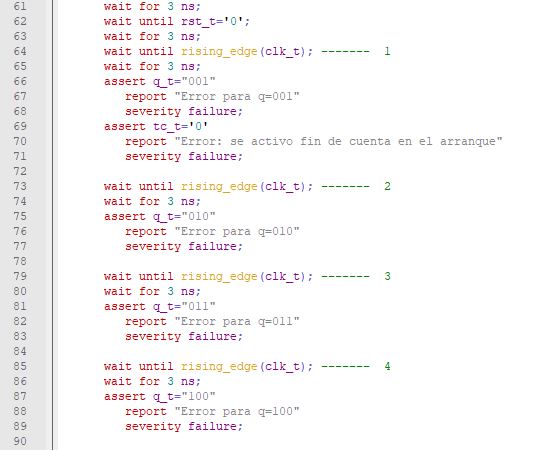

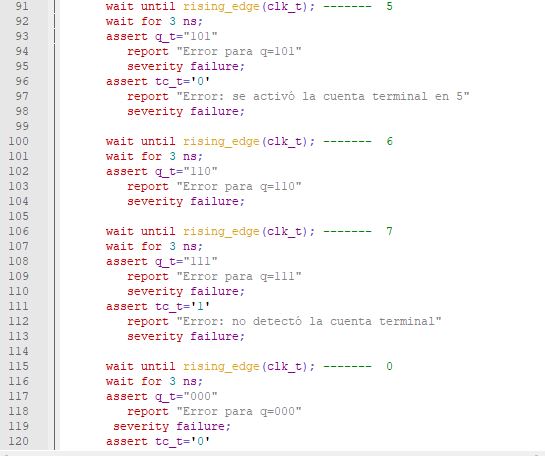

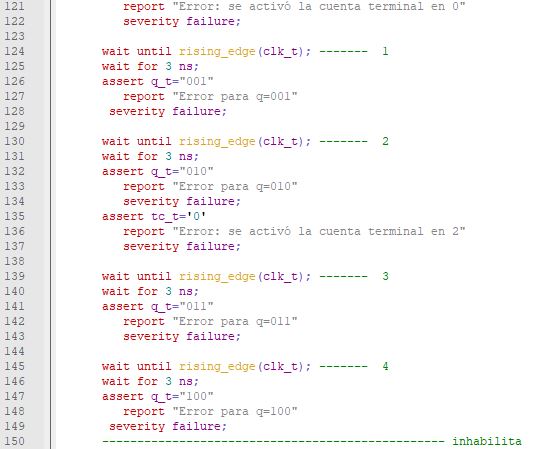

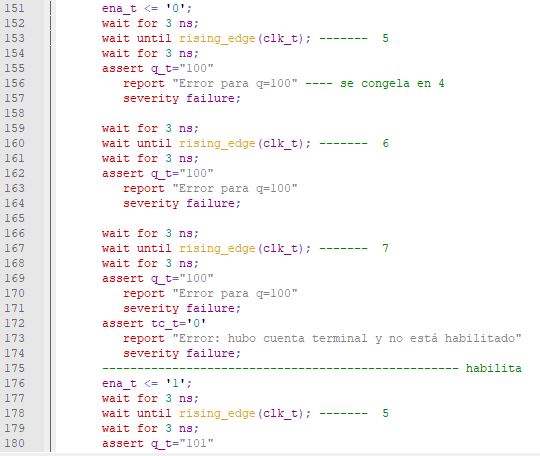

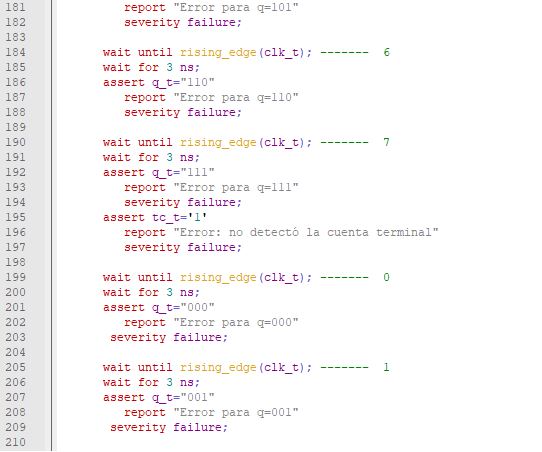

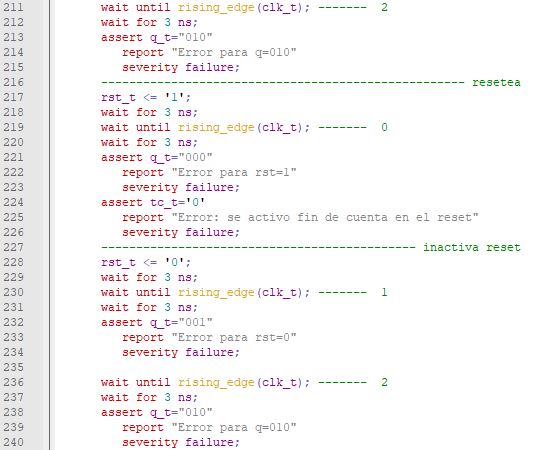

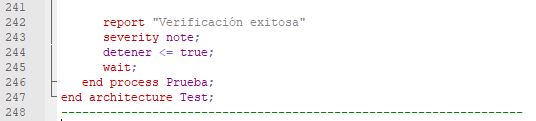

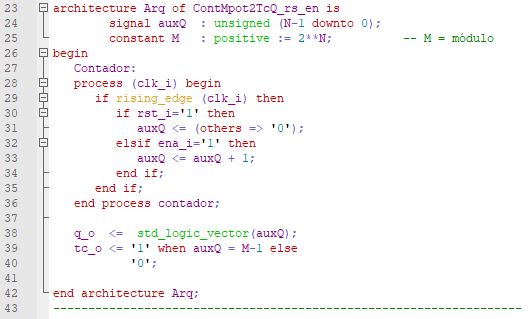

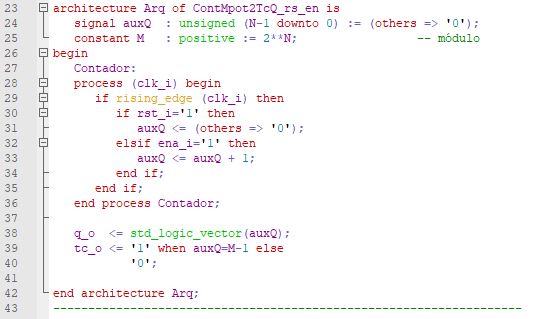

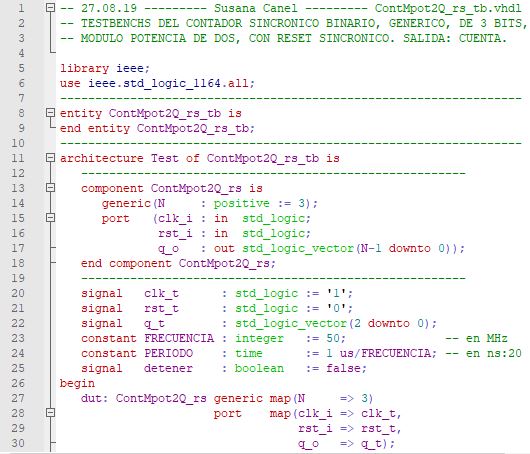

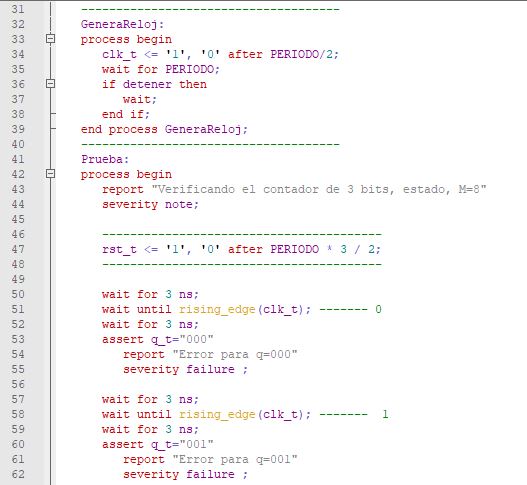

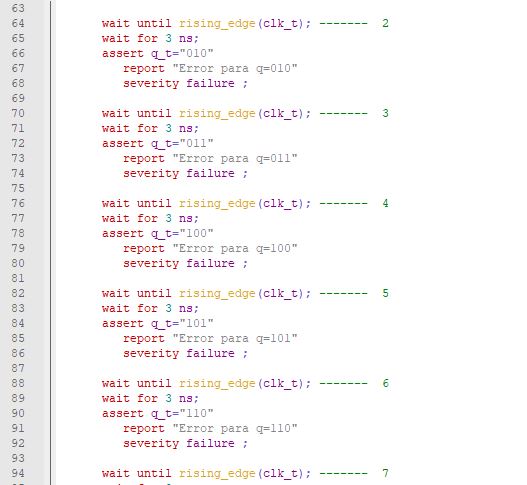

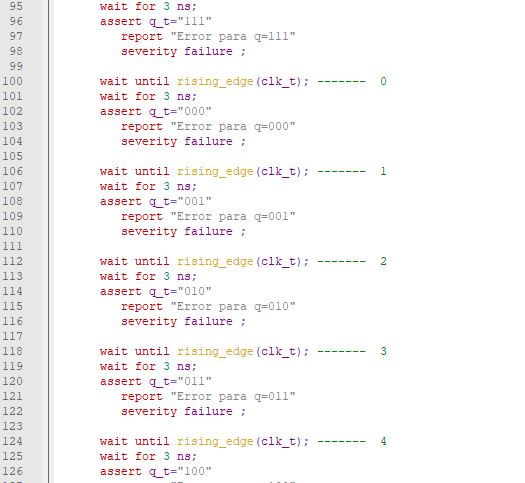

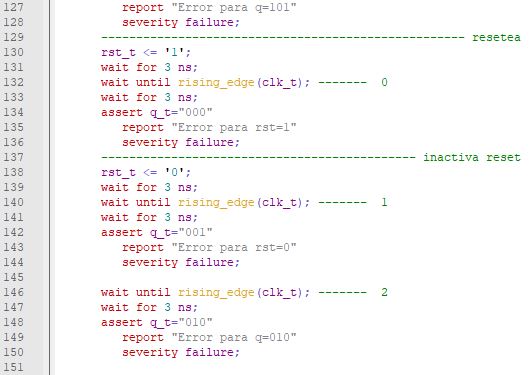

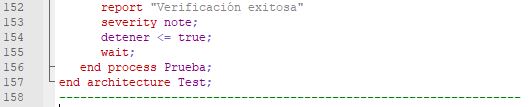

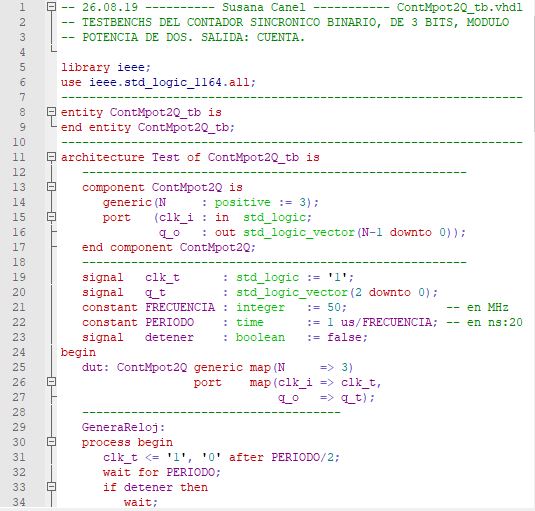

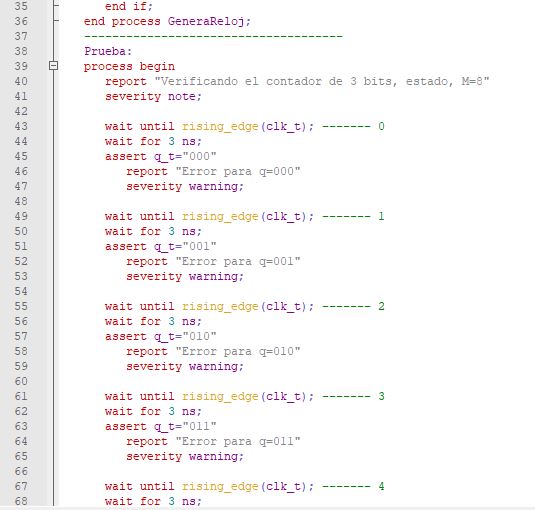

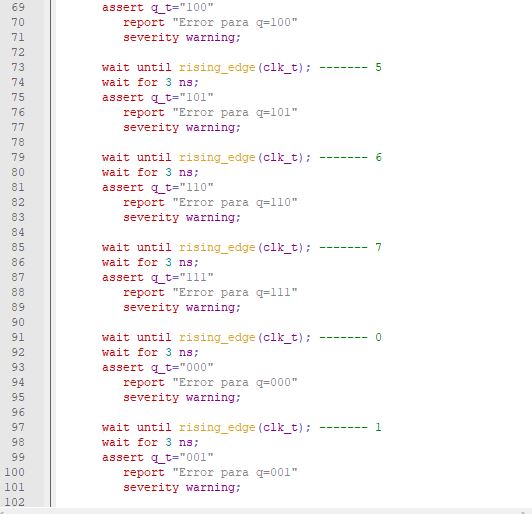

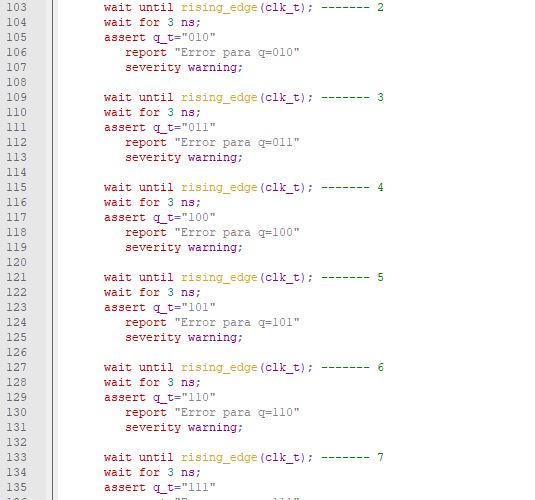

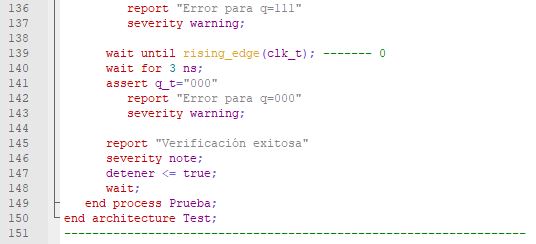

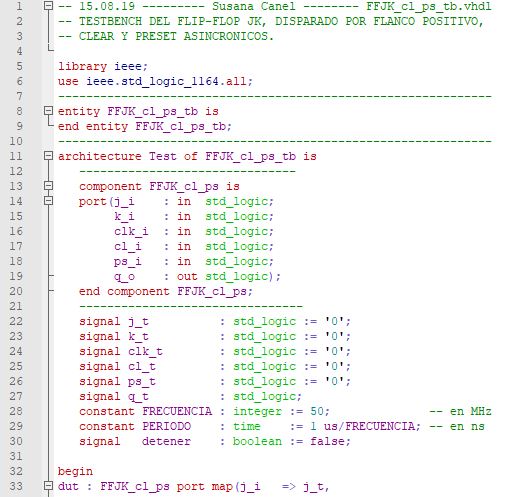

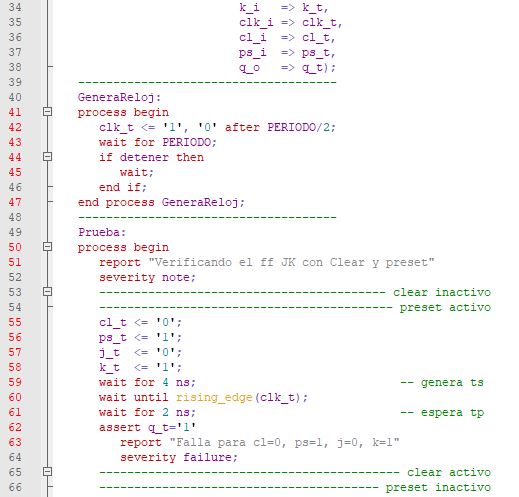

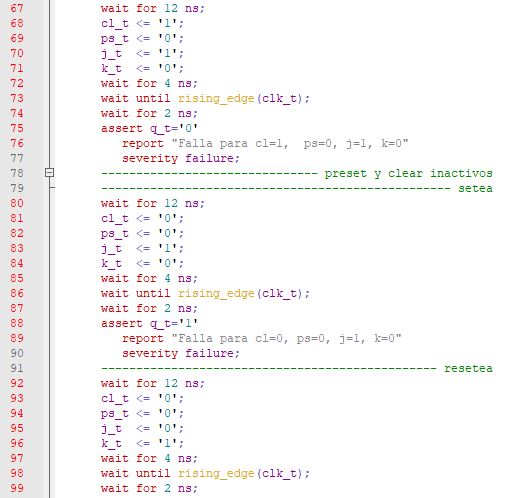

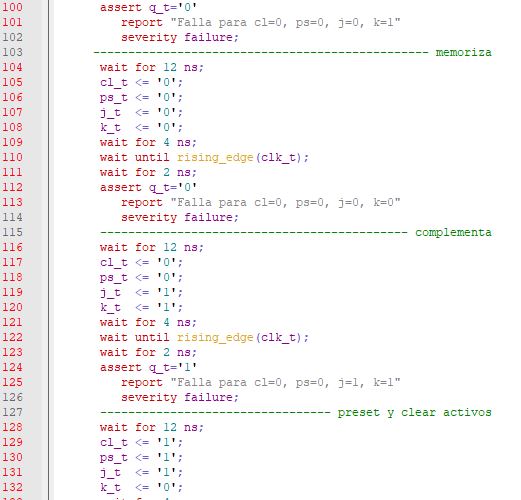

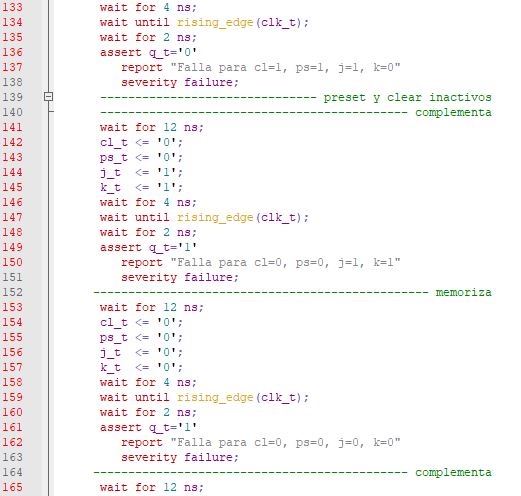

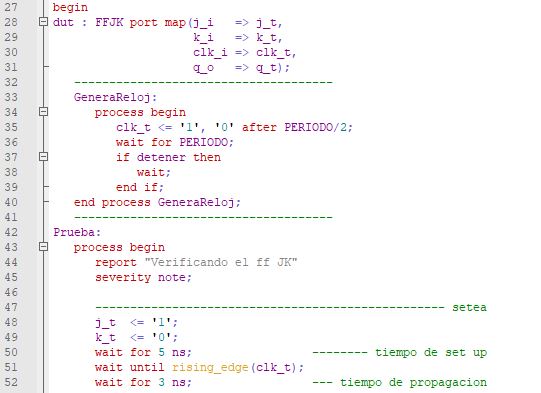

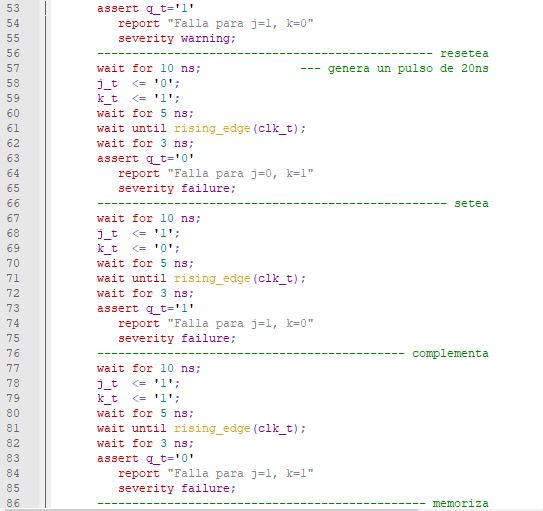

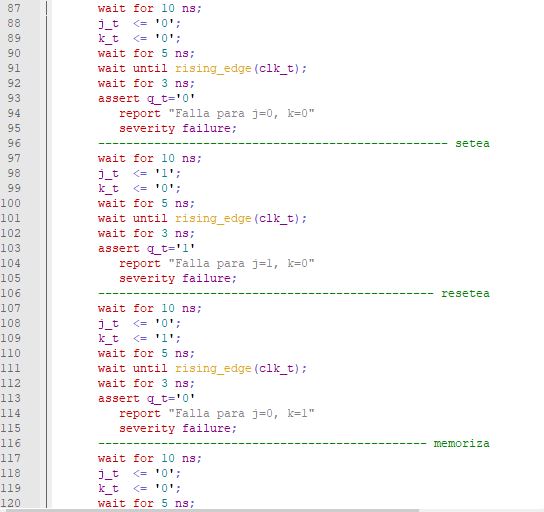

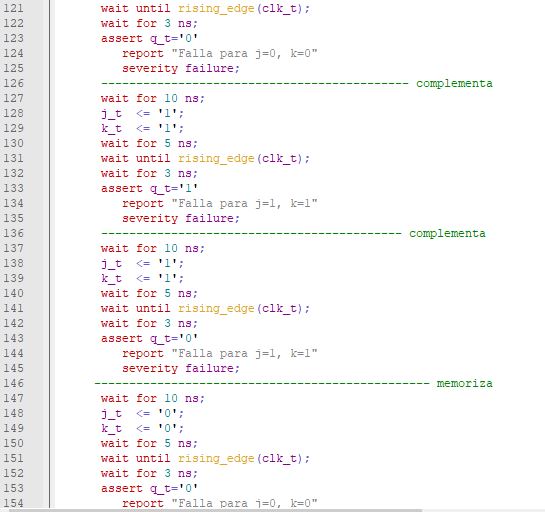

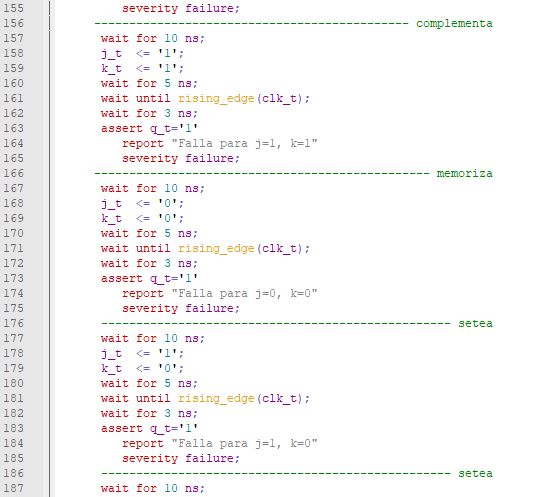

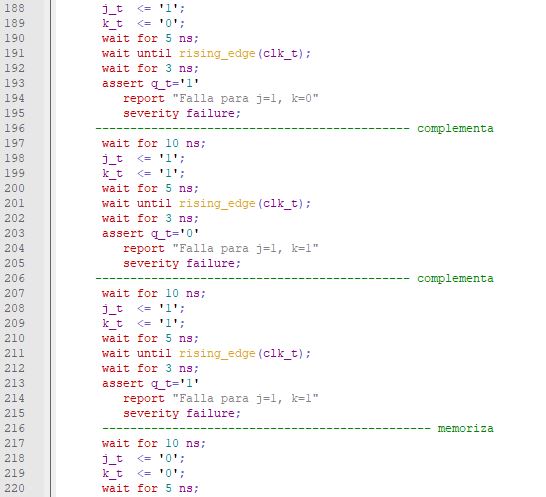

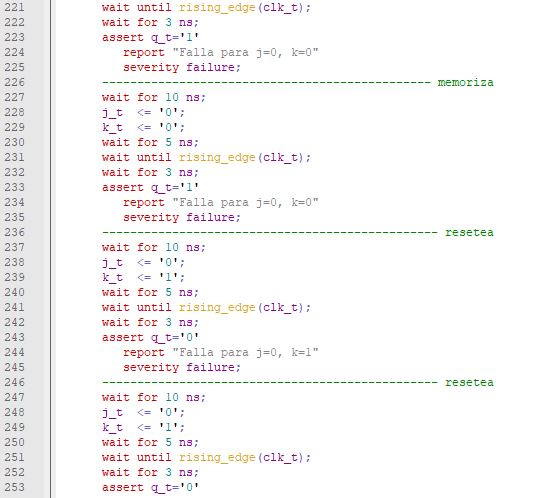

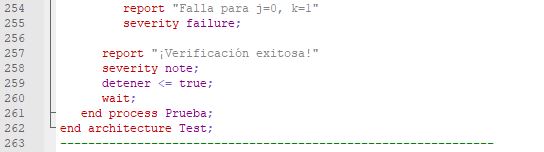

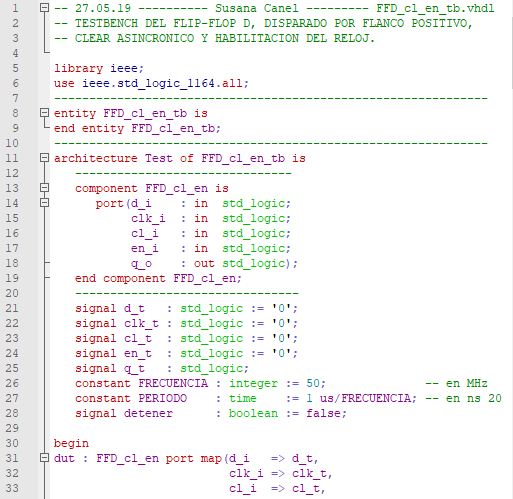

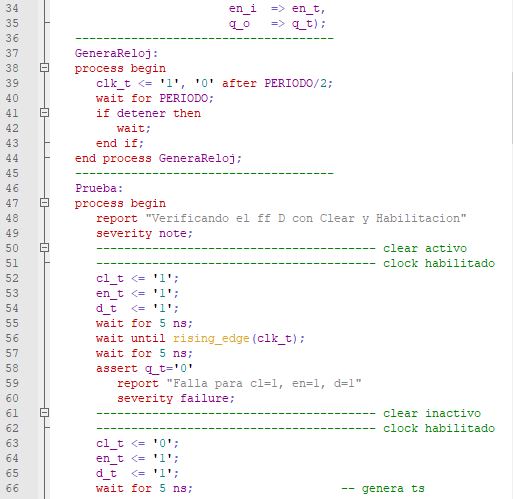

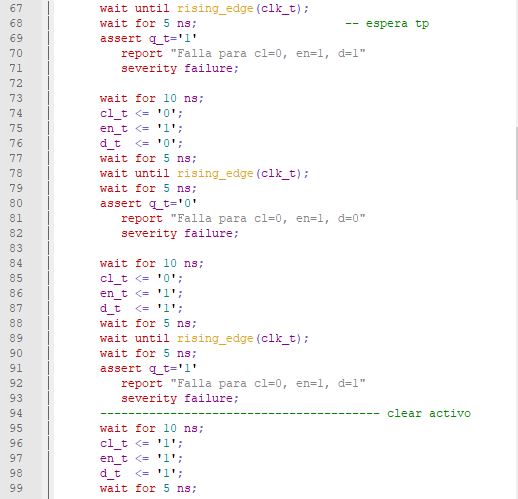

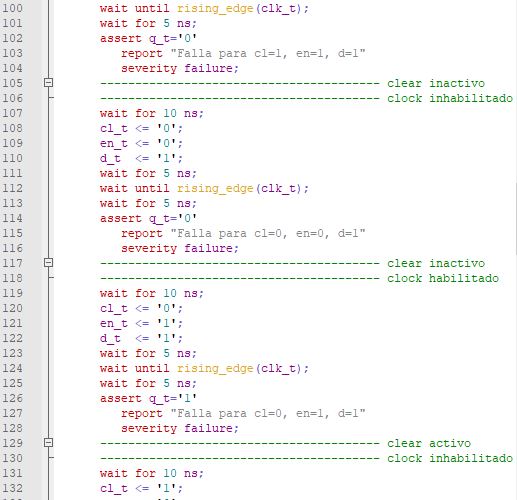

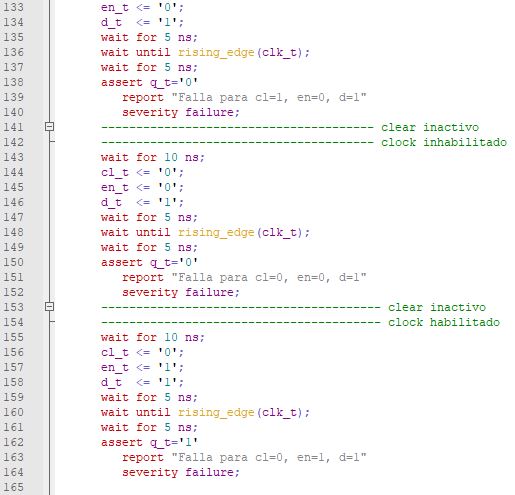

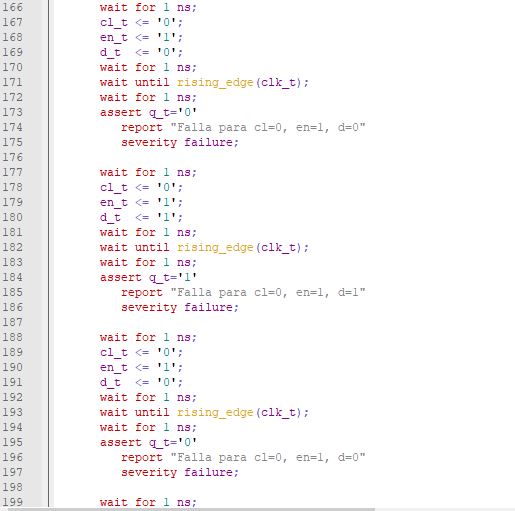

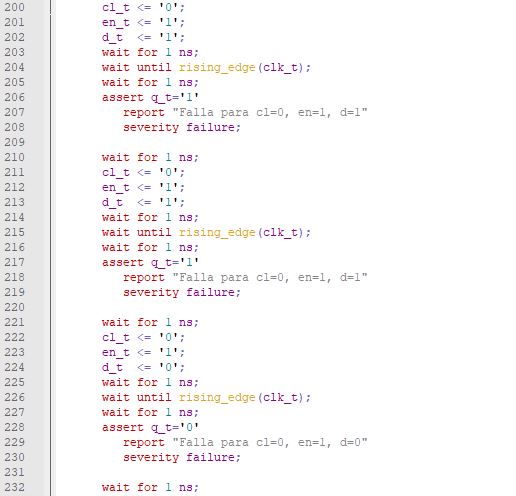

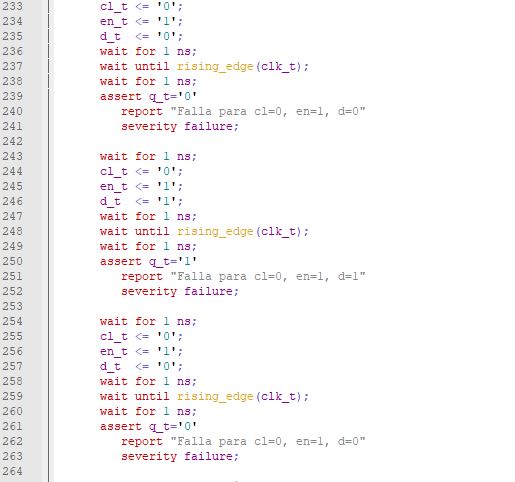

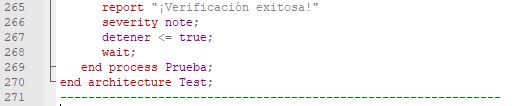

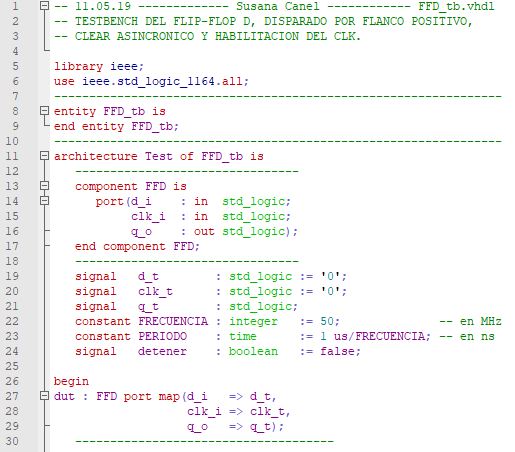

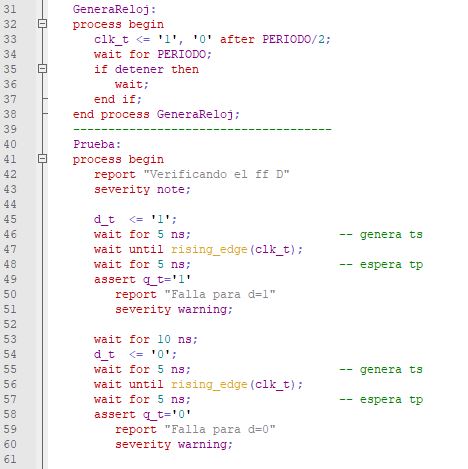

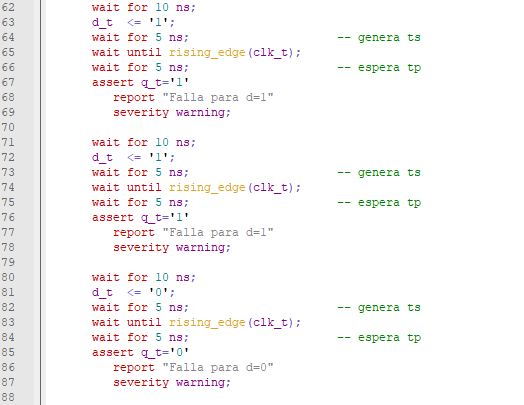

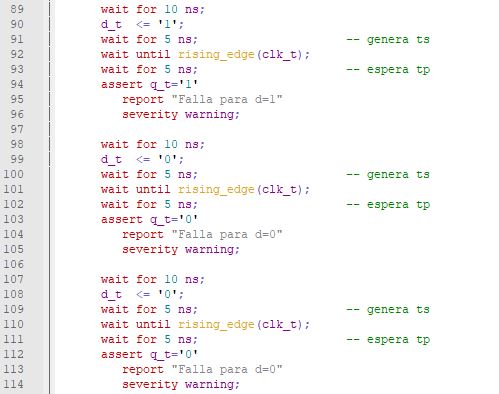

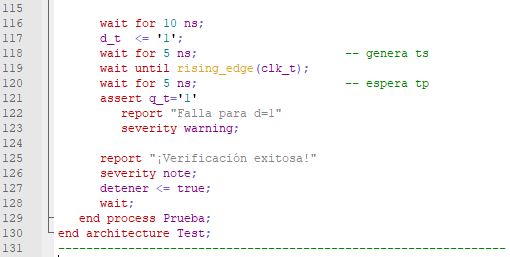

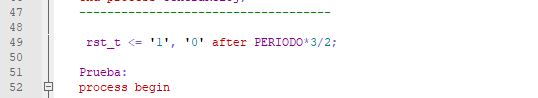

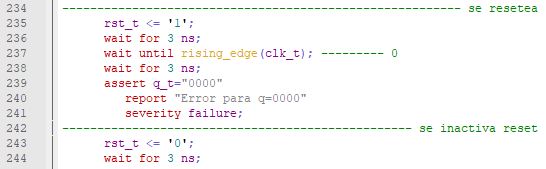

Este es el código erróneo que no se puede usar en forma simultánea:

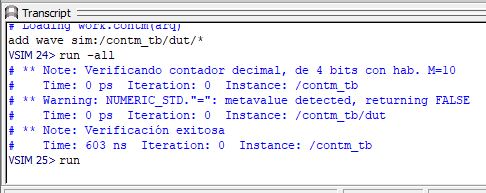

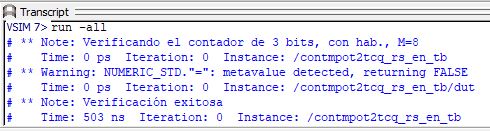

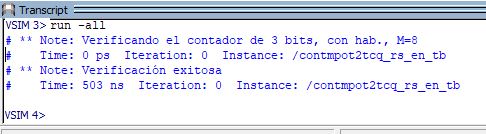

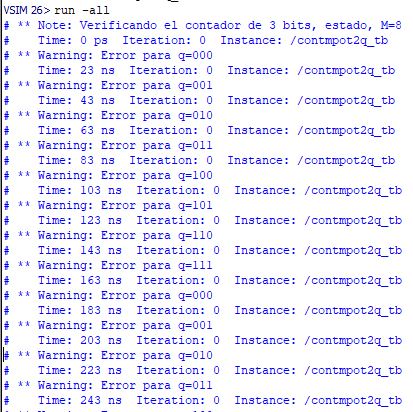

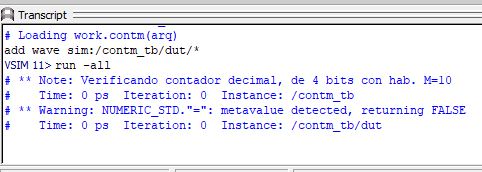

Cuando se corre la simulación la ventana Transcript se ve así:

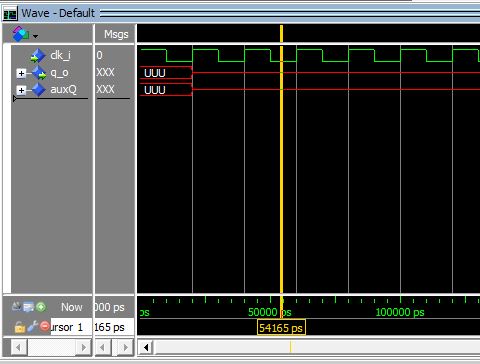

No hay información alguna sobre el resto de la simulación a partir de 0 ps. La simulación no terminó, se “colgó”. No sale ni por verificación exitosa ni por interrupción por error.

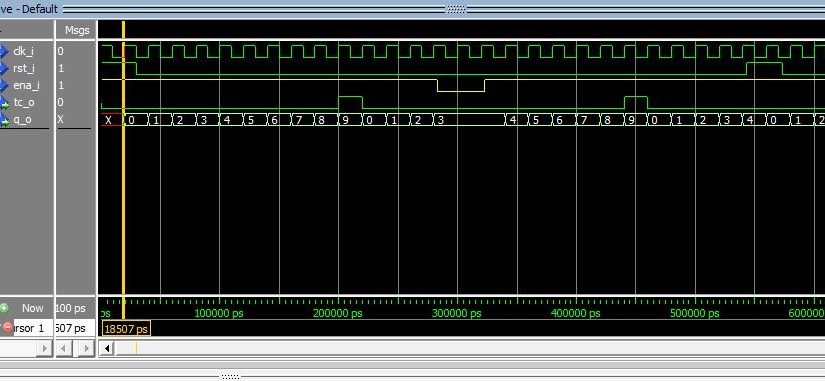

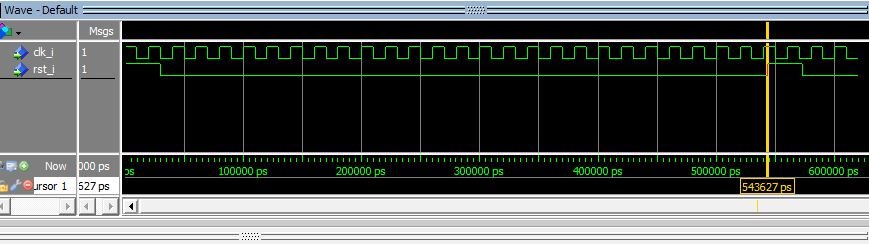

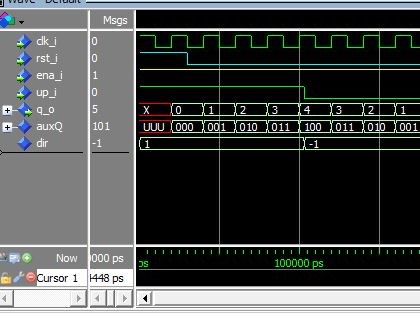

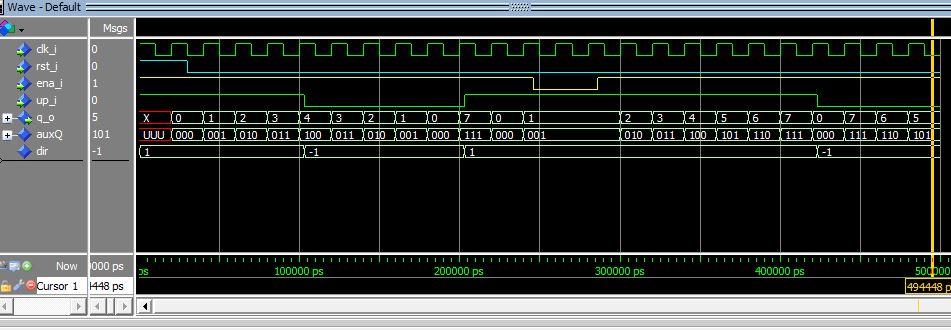

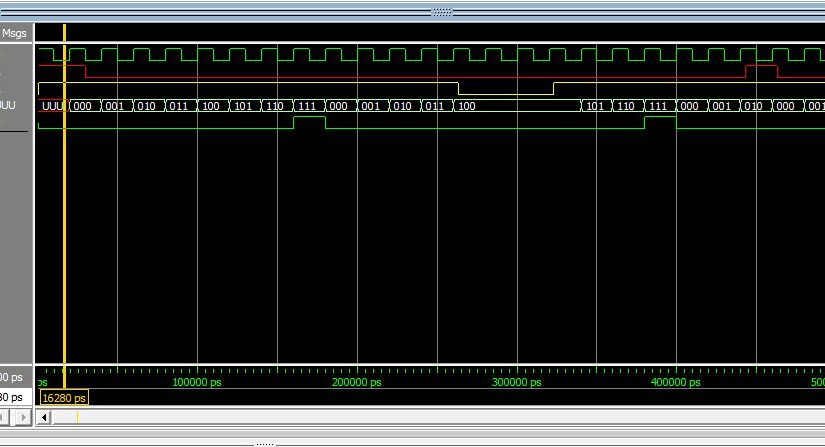

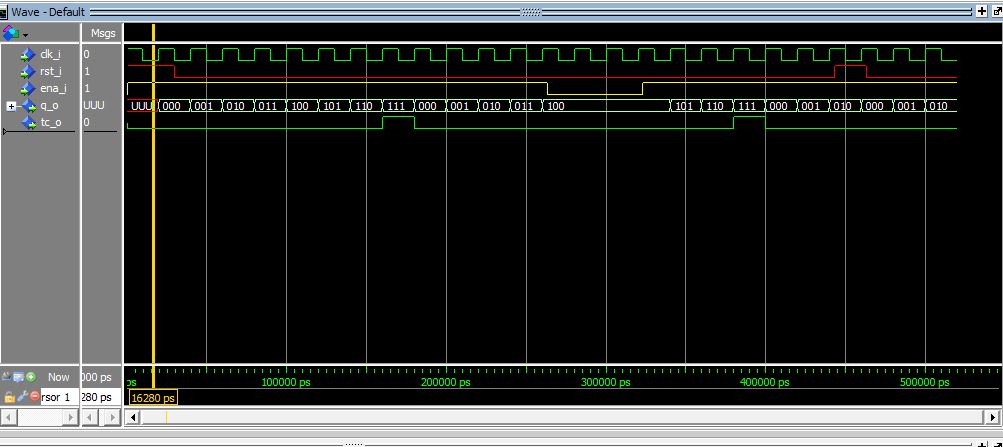

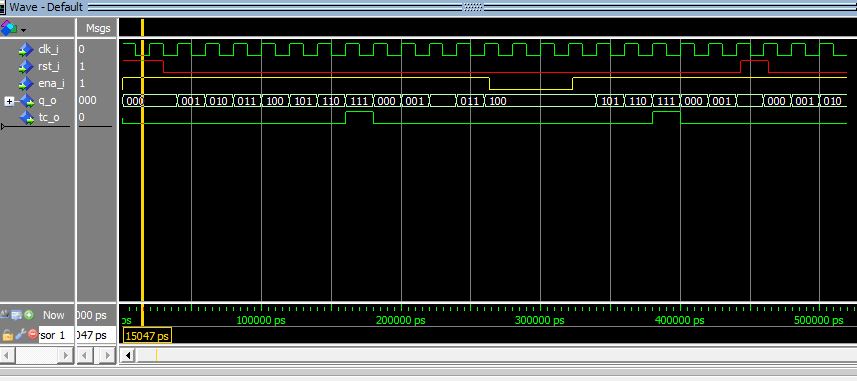

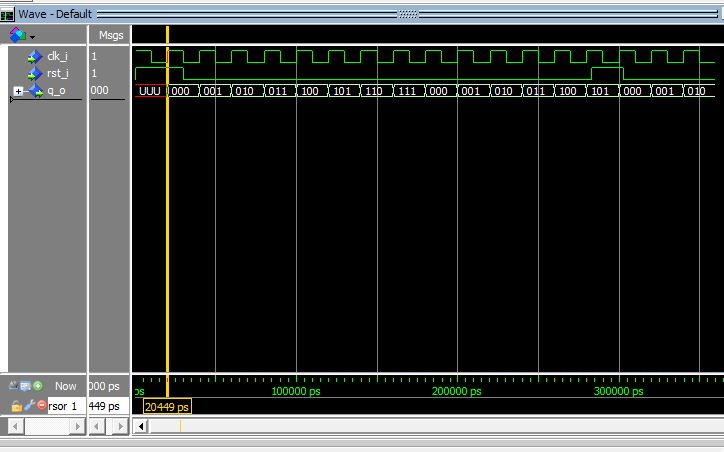

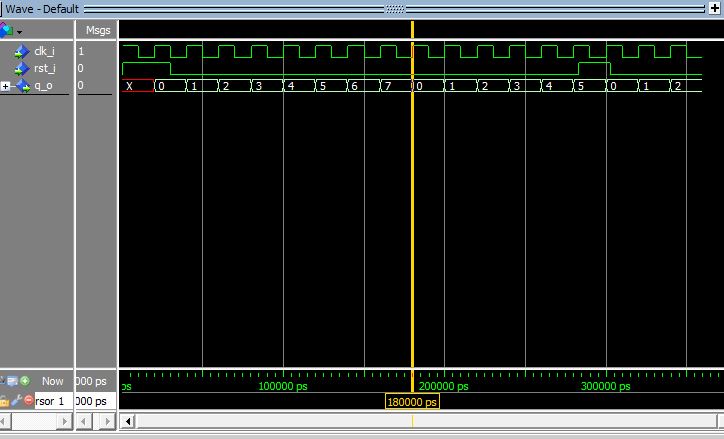

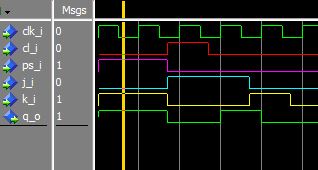

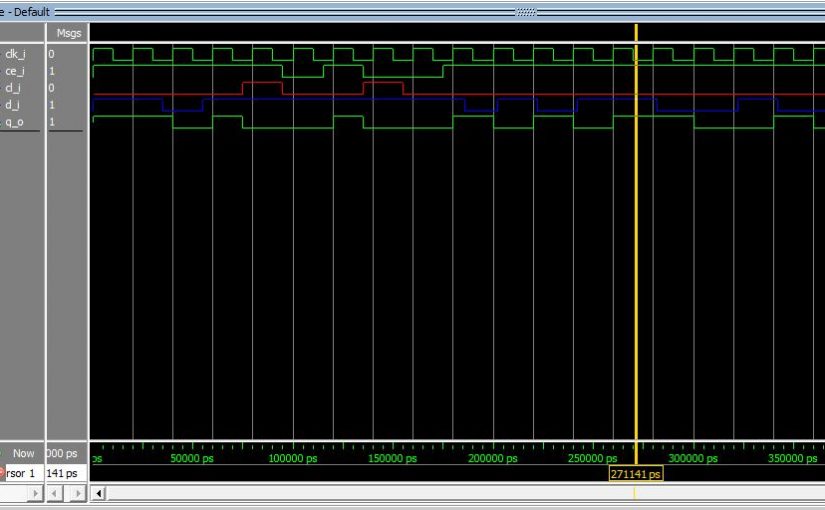

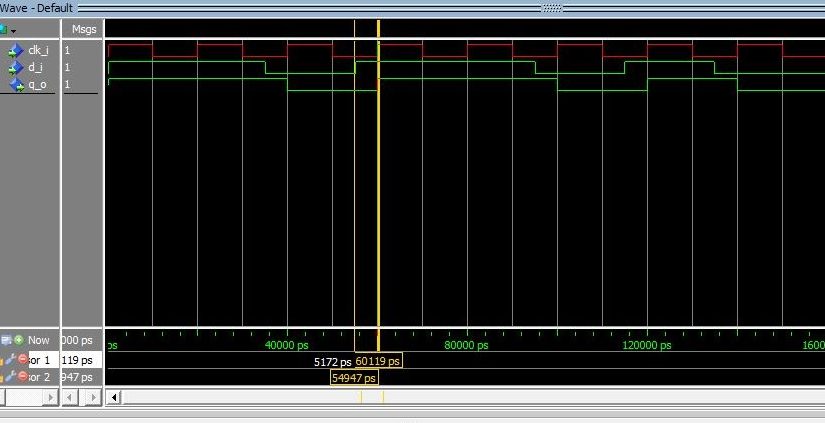

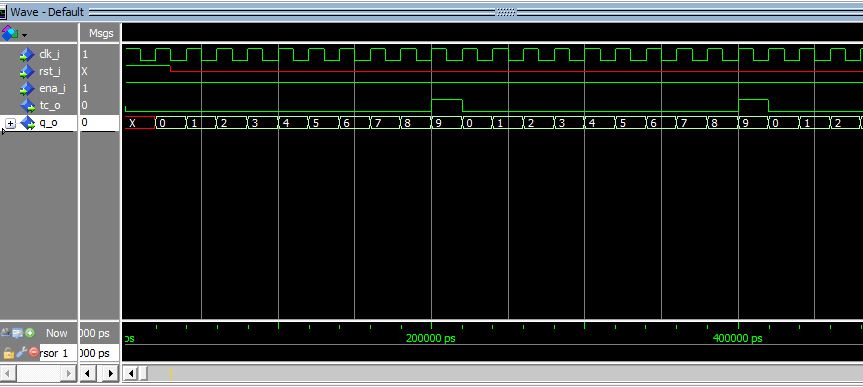

Haciendo zoom al inicio de la simulación se puede ver qué sucedió con la señal de reset. La señal de habilitación nunca cambió de estado.

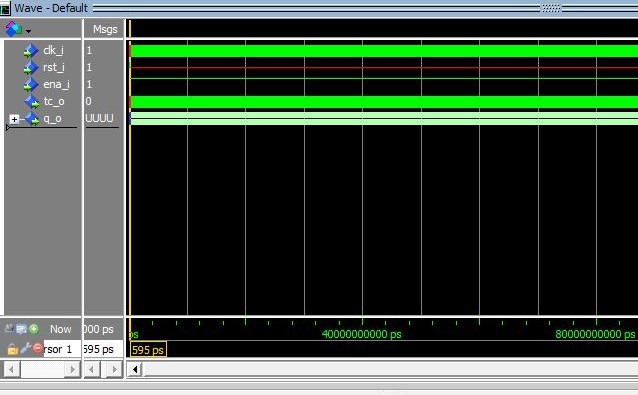

La ventana de forma de ondas antes de hacer el zoom, se veía así: