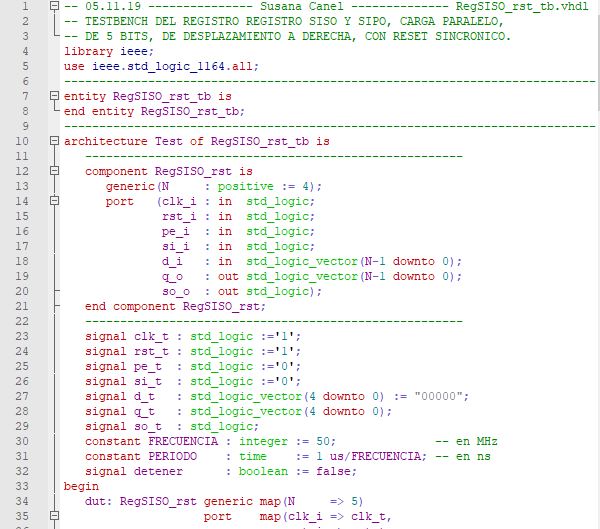

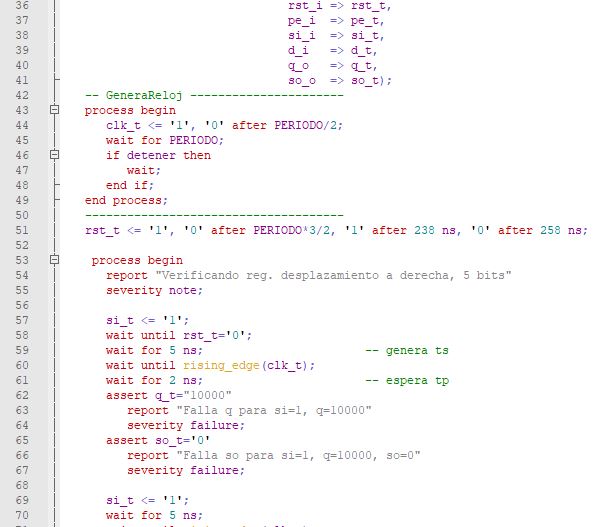

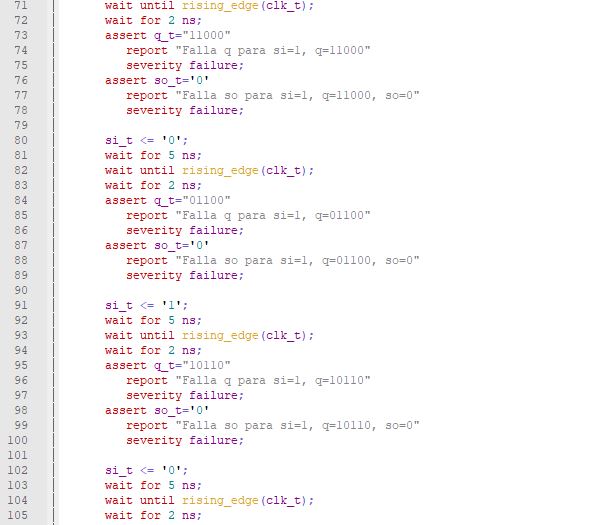

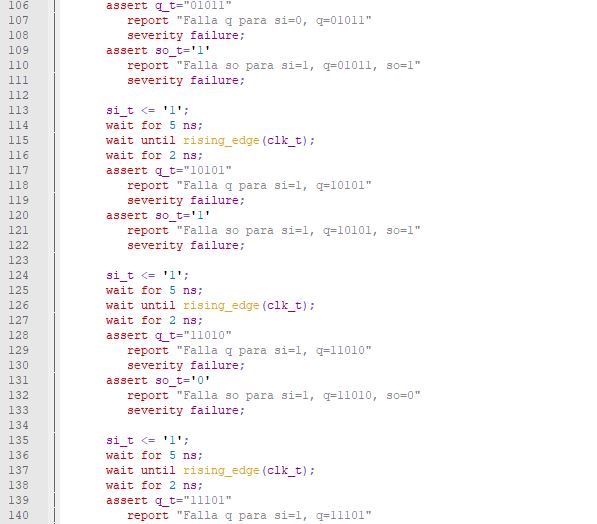

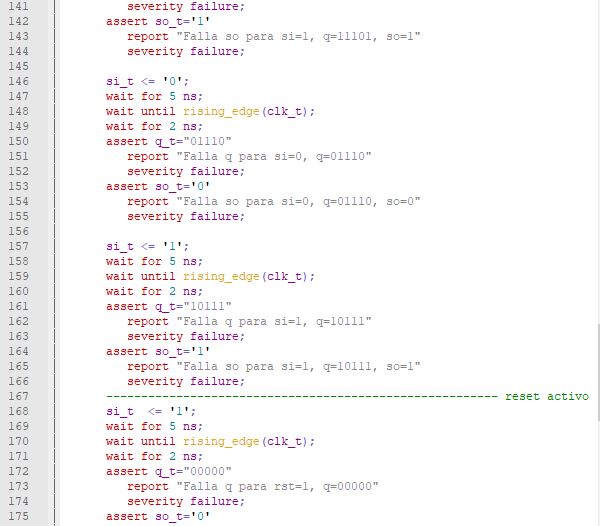

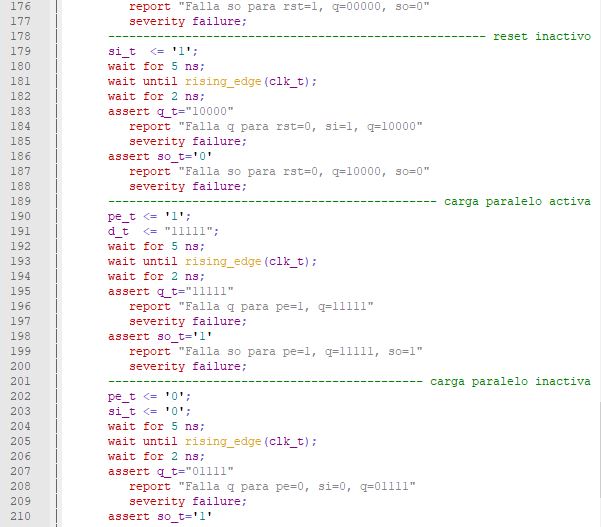

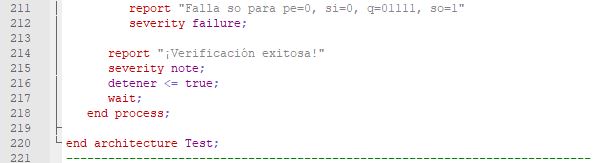

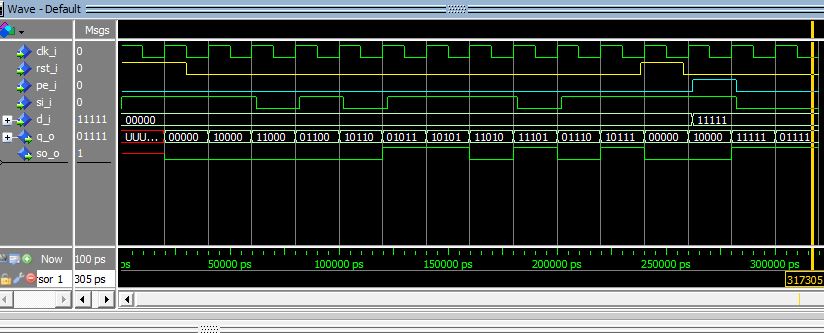

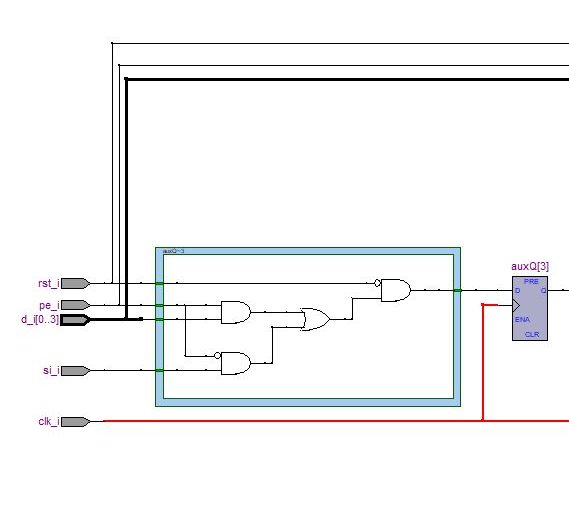

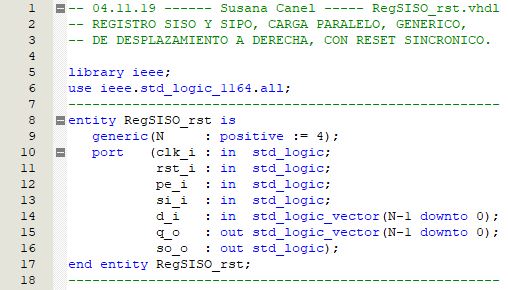

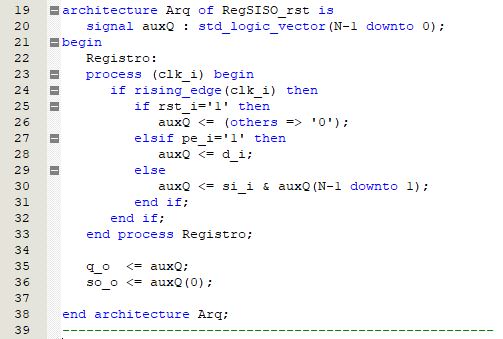

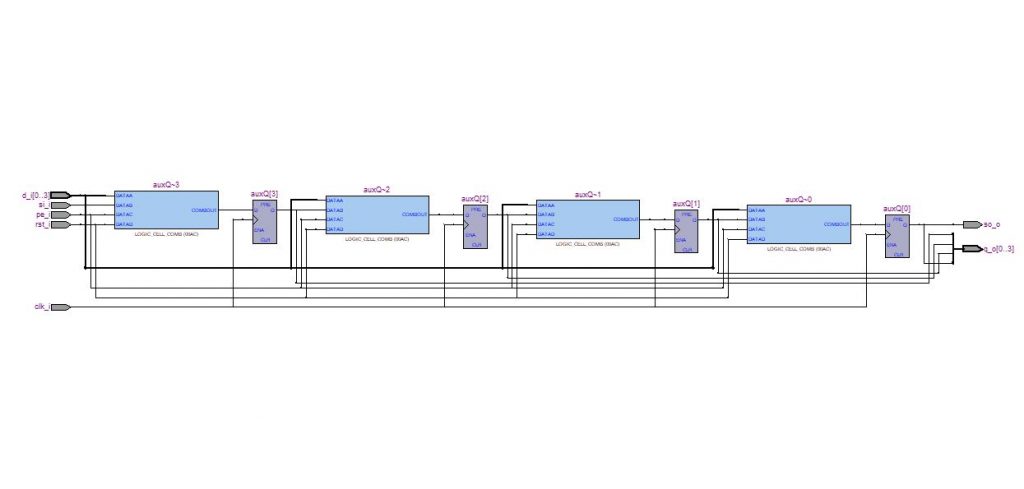

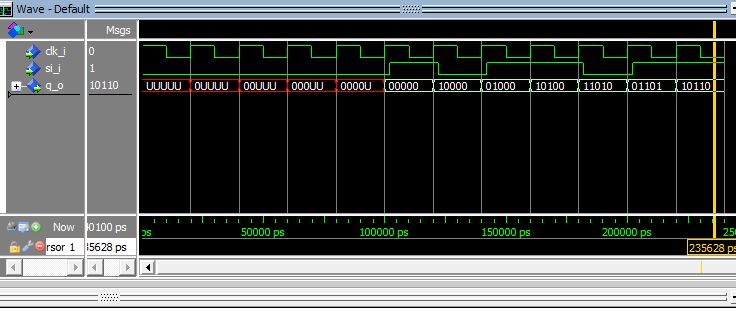

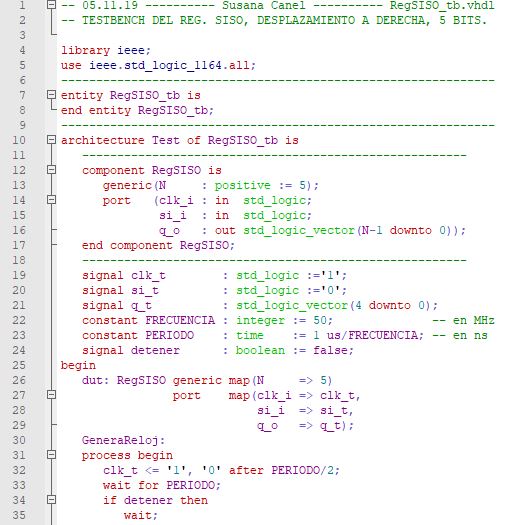

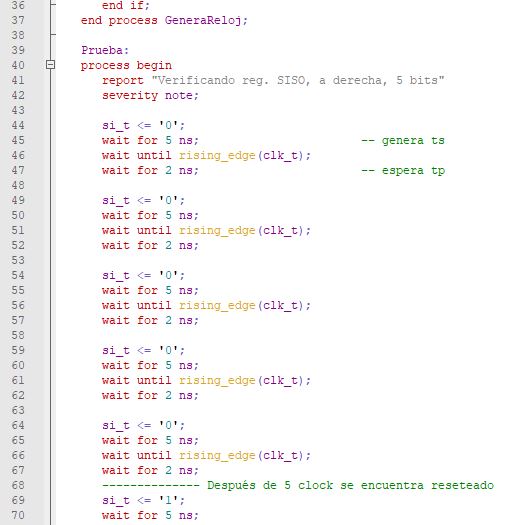

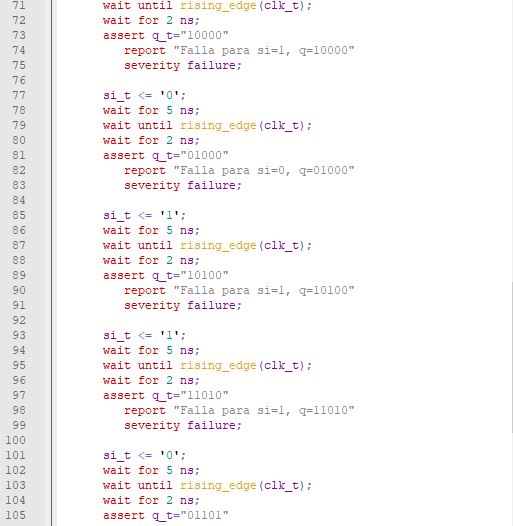

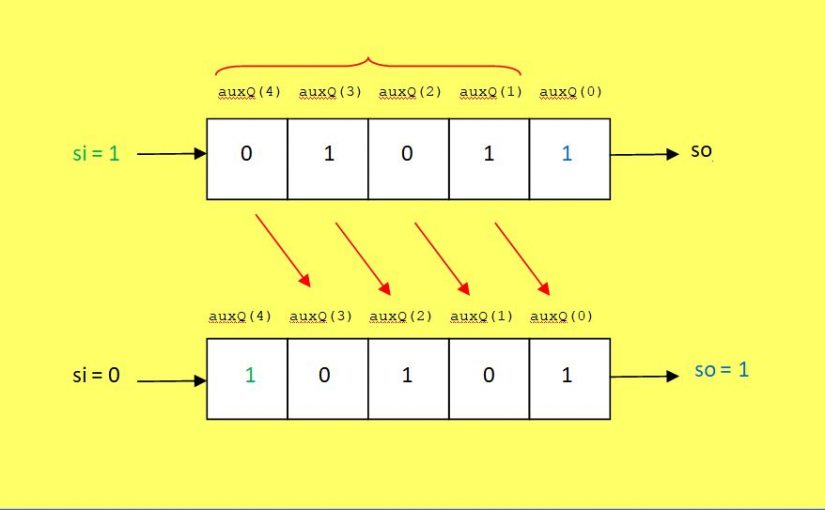

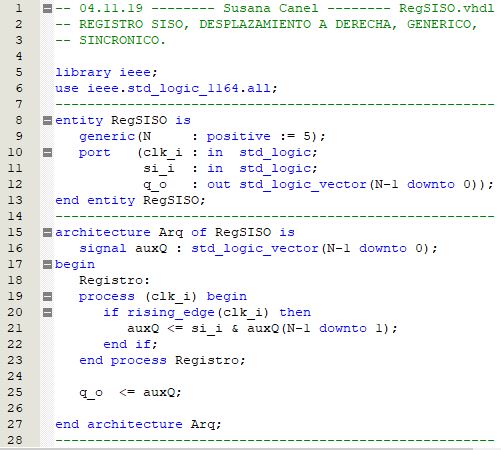

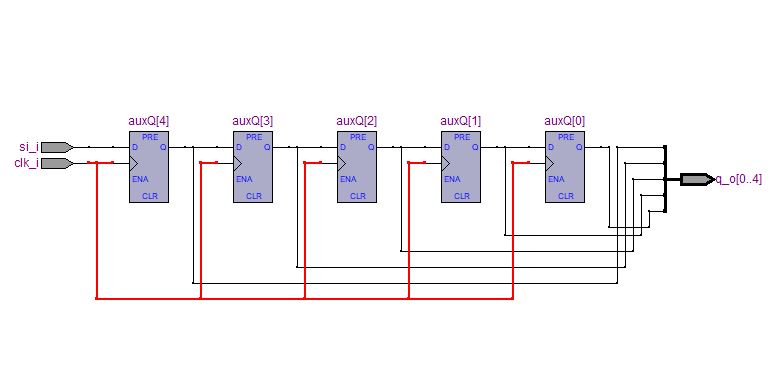

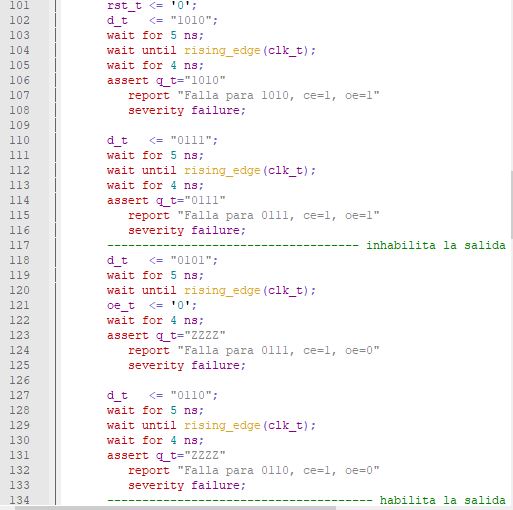

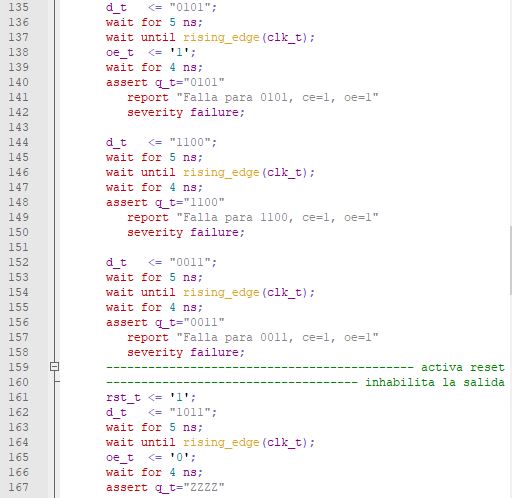

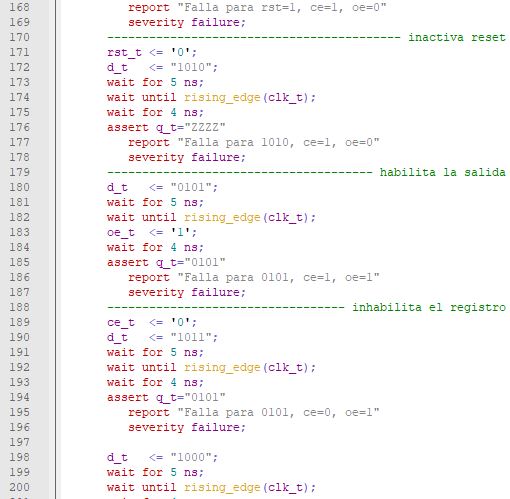

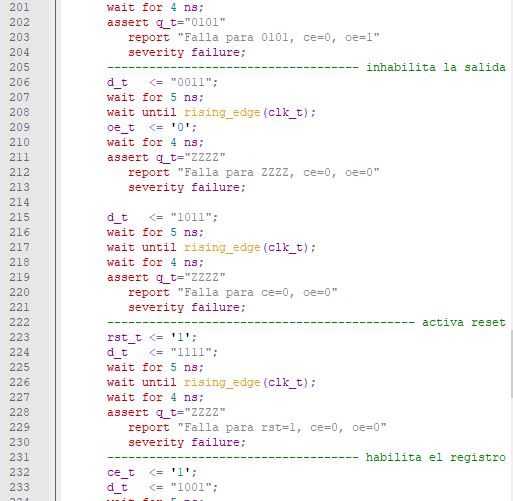

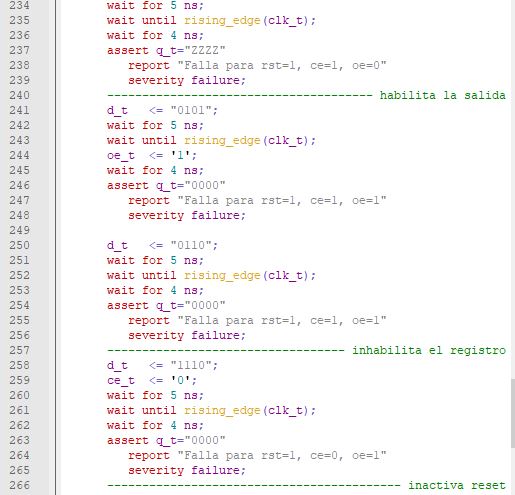

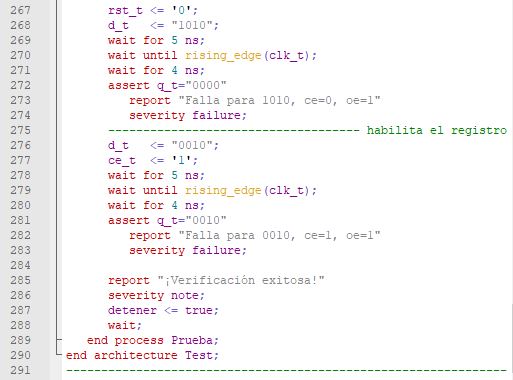

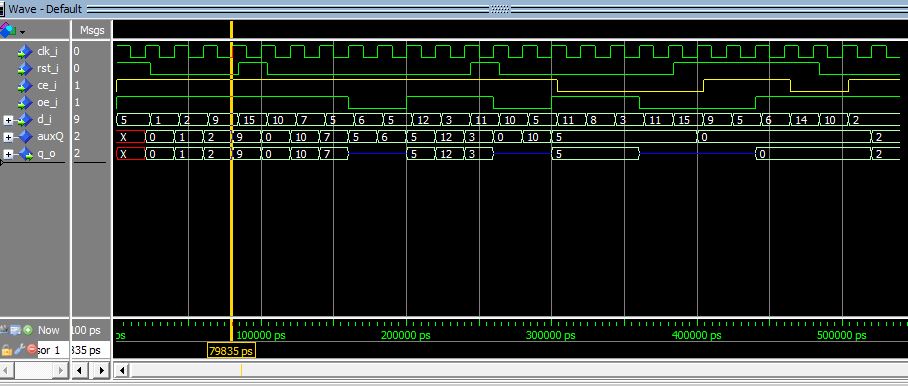

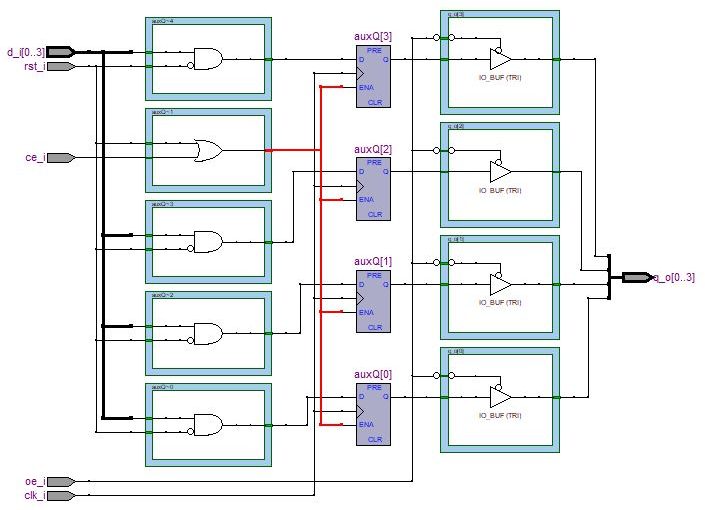

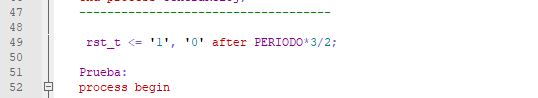

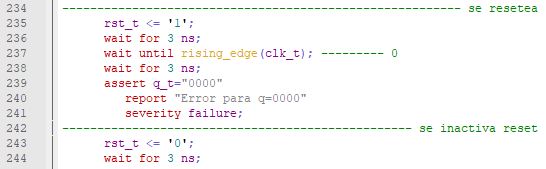

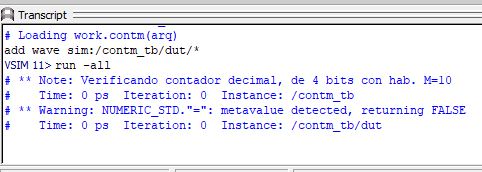

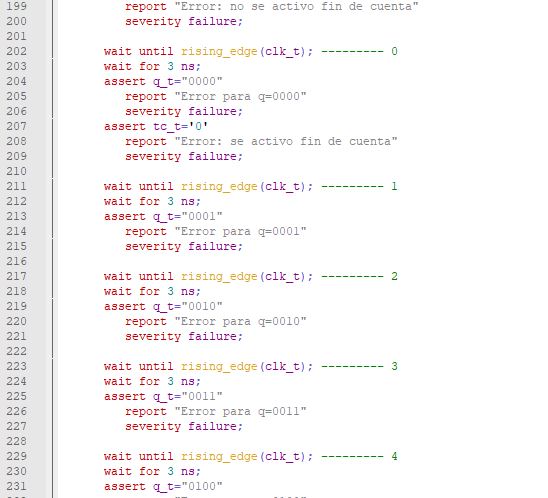

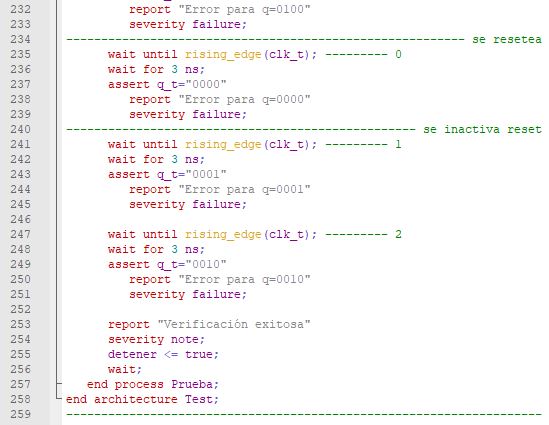

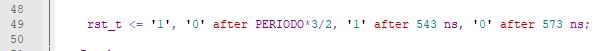

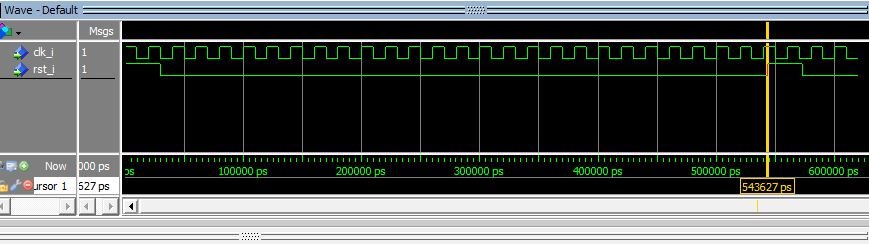

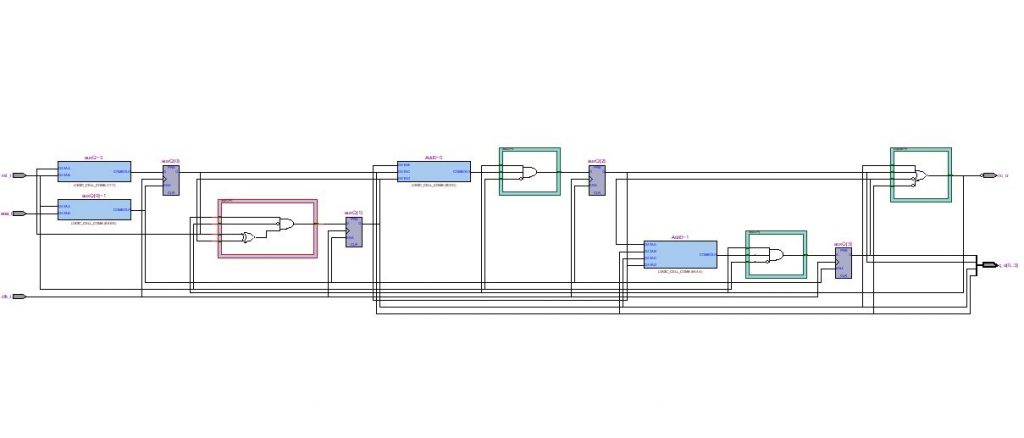

En este video te muestro el testbench de un registro de desplazamiento a derecha tipo SISO (serial input serial output) que también es SIPO (serial input parallel output), con carga paralelo, sincrónico y con reset sincrónico. Genero dos pulsos de reset usando “after”. Lo simulo con el ModelSim para comprobar el correcto funcionamiento.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entrá en /contactame/.