En este video te muestro los Netlist Viewers del Quartus II: RTL (Register Transfer Level), Technology Maps y Technology Maps (post-Mapping). Quién los genera, algunas caracterísiticas y usos.

En este video te muestro los Netlist Viewers del Quartus II: RTL (Register Transfer Level), Technology Maps y Technology Maps (post-Mapping). Quién los genera, algunas caracterísiticas y usos.

En este video te muestro cómo simular el comportamiento de un decodificador de 3 entradas a 8 salidas. Vemos cómo generar la entrada de habilitación para que habilite al decodificador y lo inhabilite durante algunos pulsos. Qué estímulos conviene dar a las señales de entrada. Y particularidades del editor del simulador. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video te muestro de dónde descargar en forma free el software Quartus II, de la empresa Intel (Intel compró a la empresa Altera). Te explico qué versión voy a usar al principio del curso y porqué. Por pedido te puedo enviar los archivos de texto para que puedas practicar con ellos. Te espero en el próximo video.

Con este video inicio la Lección 2, que corresponde a descripciones VHDL de dispositivos combinacionales de propósitos generales o MSI. Describo un decodificador de 3 entradas a 8 salidas activas en alto, con entrada de habilitación también activa en alto. Uso las sentencias with-select para generar la tabla de verdad y las sentencias when else para poner la condición de habilitación. Uso when-others para cubrir todos los casos y la expresión (others =>’0′) para generar un std_logic_vector en 0 sin tener que conocer la dimensión del vector (el software ya posee esa información). Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video te explico cómo describir una compuerta AND de 2 entradas con una tabla de verdad en forma comprimida mediante un puntero. Mantengo la entidad de los diseños anteriores, genero un vector con las dos entradas para lo cual las tengo que concatenar, como ya vimos en un ejemplo anterior. Y defino una “signal” de tipo “std_logic_vector”. Para hacer el “casting” incorporo un nuevo package: “numeric_std“. Defino una constante en la parte declarativa de la arquitectura y muestro cómo se hace un “casteo“. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video te muestro qué sucede si hacemos simulación “timing” en lugar de “functional”. Vemos cómo influyen los tiempos de propagación de las señales en un dispositivo real y por qué usamos la simulación “functional” para poder analizar la lógica de nuestro diseño o sea el comportamiento ideal, en un dispositivo con tiempo de propagación nulo. Después te muestro cómo agrupar señales para usarlas como elementos de un vector. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video te explico cómo describir el comportamiento de una compuerta AND de 2 entradas como tabla de verdad usando las sentencias with-select que son las adecuadas para definir tablas. Mantengo la entidad de los diseños anteriores, genero un vector con las dos entradas para lo cual las tengo que concatenar. Y defino una “signal” de tipo “std_logic_vector”. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video repasamos el uso del Quartus II para realizar una descripción y la sintaxis de la descripción incorporando la sentencia when-else que se caracteriza por ser condicionada y generar prioridad dada por el orden en que se pone la condición. Si hay varias condiciones no son mutuamente excluyentes. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

En este video les muestro cómo se compila usando el Quartus II y cómo se simula usando la versión 9.1 que traía un simulador incorporado. No se trata de una simulación profesional pero sí de una herramienta didáctica para un curso de nivel inicial. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

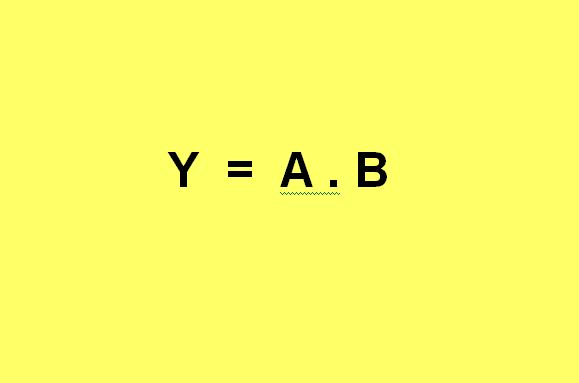

¡Hola! Con este primer video comienzo a explicarte cómo diseñar con VHDL. Diseñaré una compuerta AND de 2 entradas por medio de ecuaciones. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/