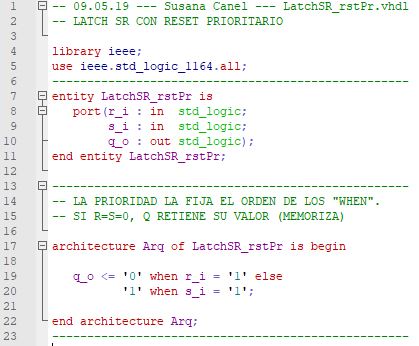

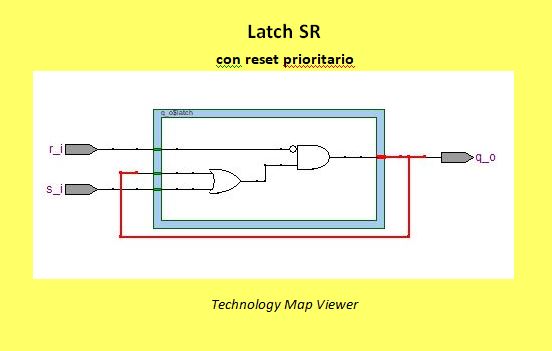

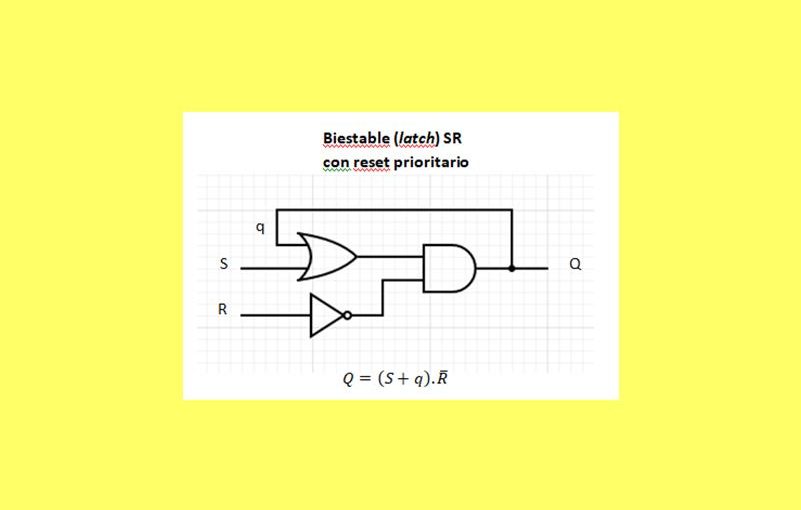

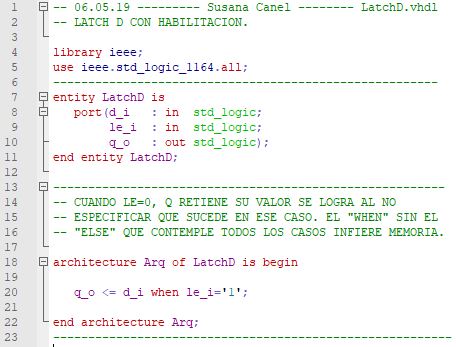

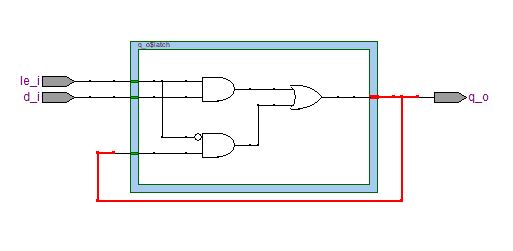

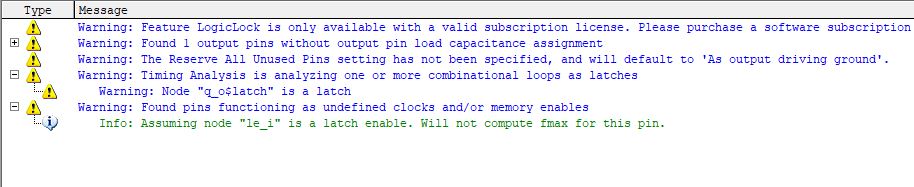

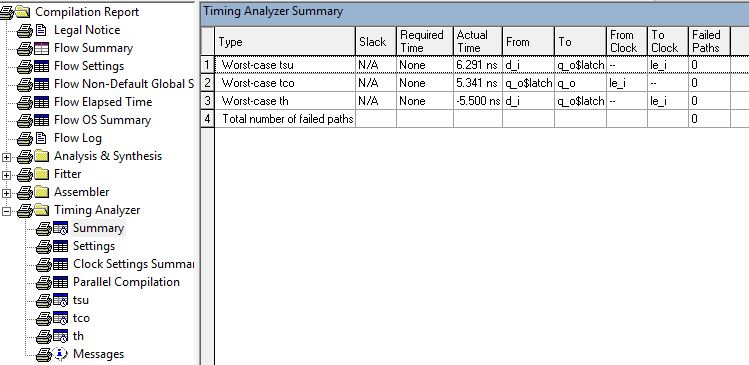

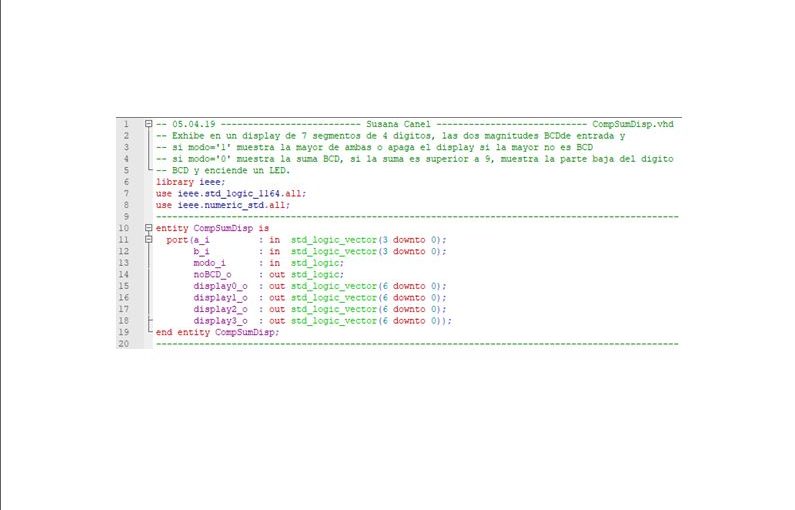

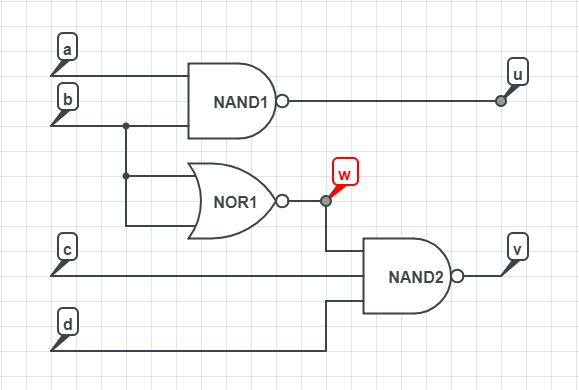

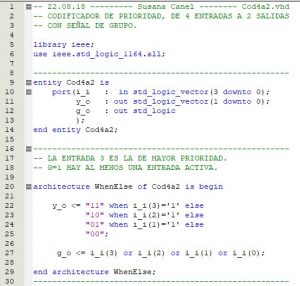

En este video te muestro la descripción de un latch SR con reset prioritario. Uso la sentencia condicionada “when…else” para generar la prioridad y al usarla incompletamente especificada infiero memoria. Compilo. Analizo los “warnings” y te muestro el esquemático generado con la herramienta “Technology Map Viewer” del “Tool” del Quartus II. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/