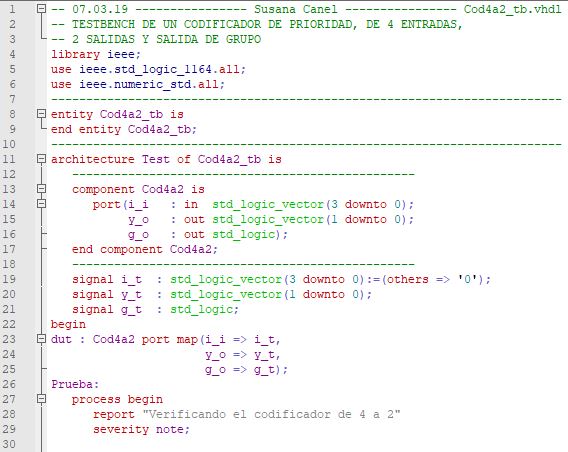

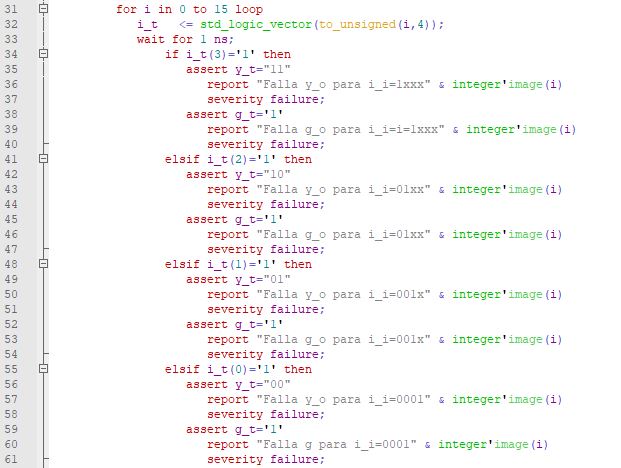

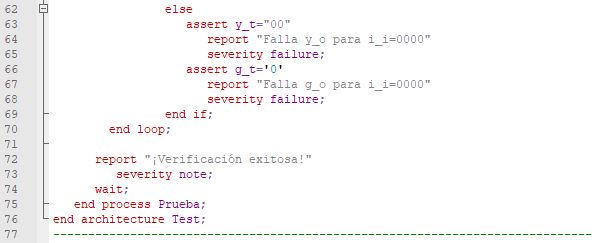

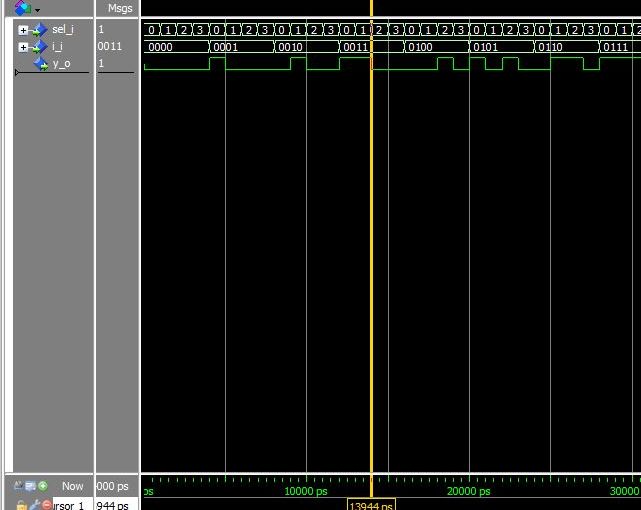

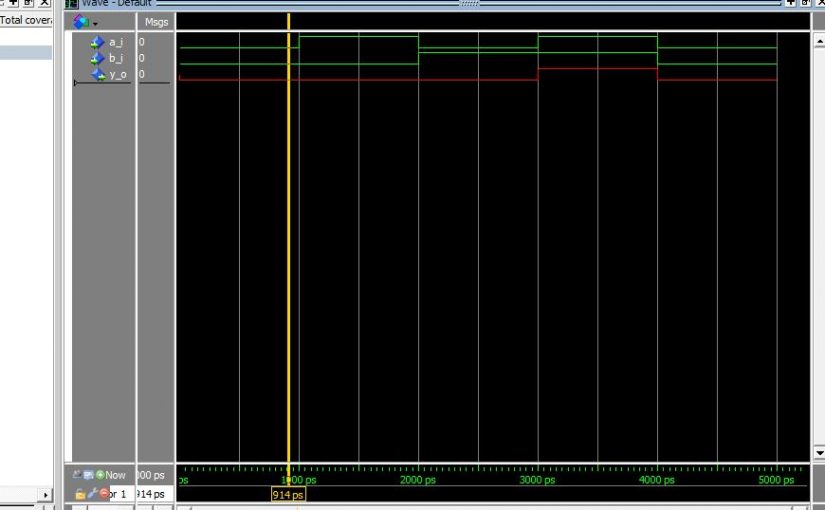

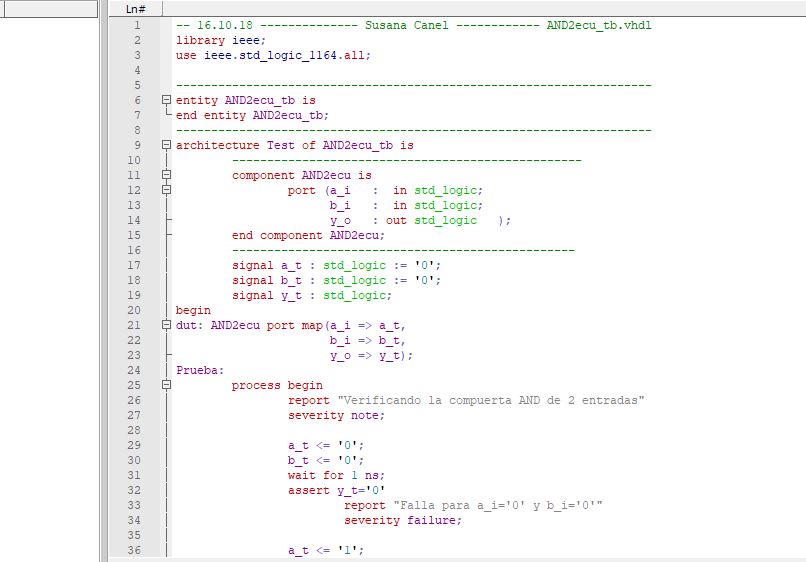

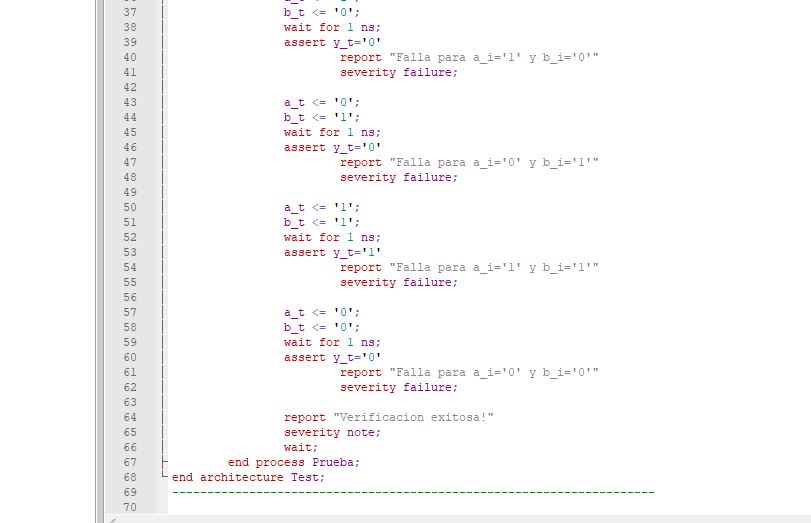

En este video te explico un banco de pruebas (testbench) para un codificador de prioridad de 4 entradas a 2 salidas codificadas y señal de grupo. Uso el ModelSim de Intel-Altera, versión 10.5b. Uso un ciclo “for-loop” y dentro de éste la sentencia “if” con las opciones “elsif” y “else”. Compilo y para finalizar uso el testbench para simular y te muestro el resultado.

A través de “contactame” /contactame/ puedes pedirme que te envíe los archivos de texto con las descripciones y testbenchs para que los puedas probar y el tutorial del Quartus II, que hice.