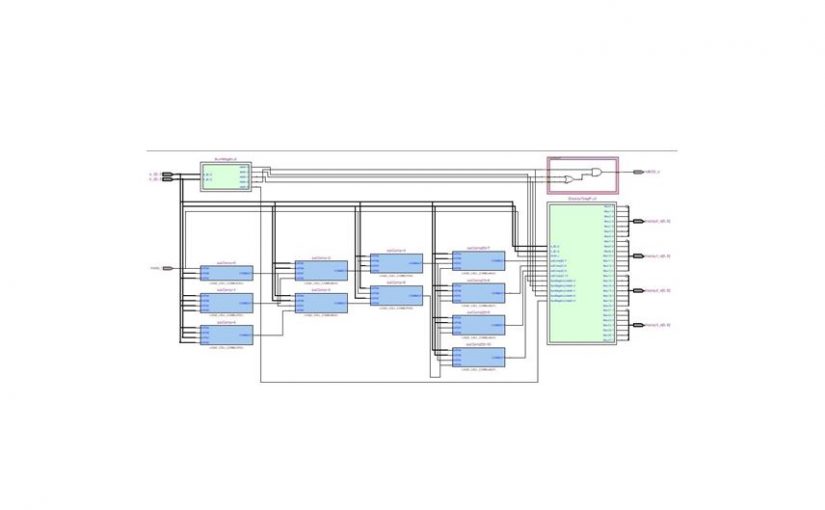

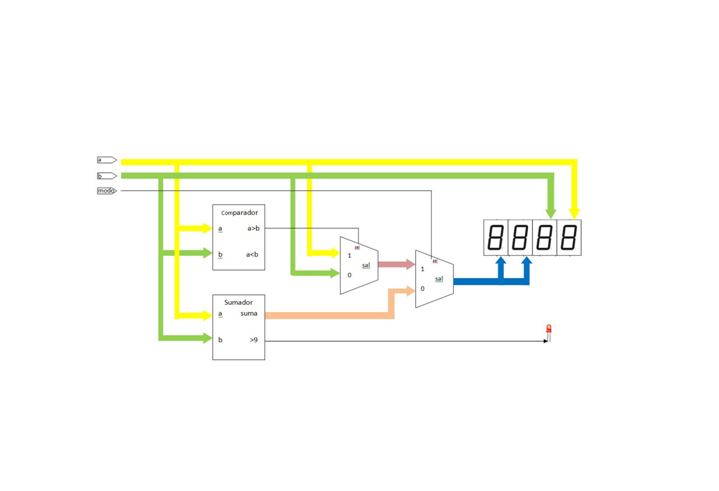

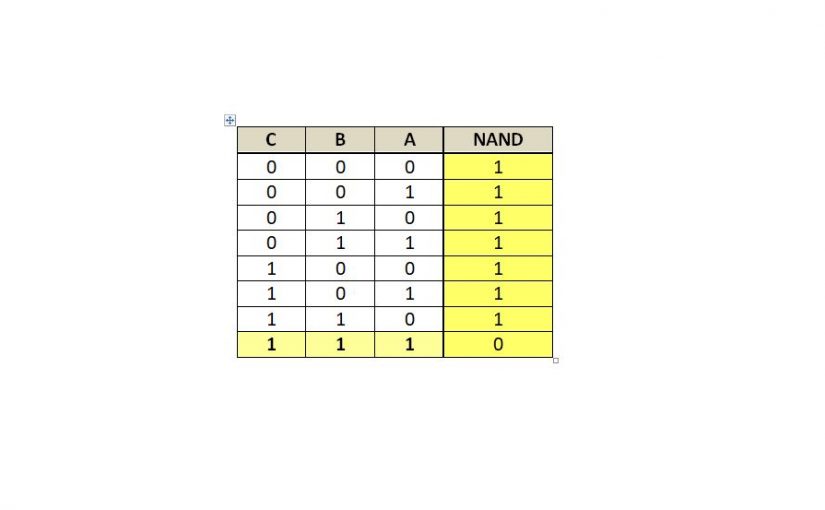

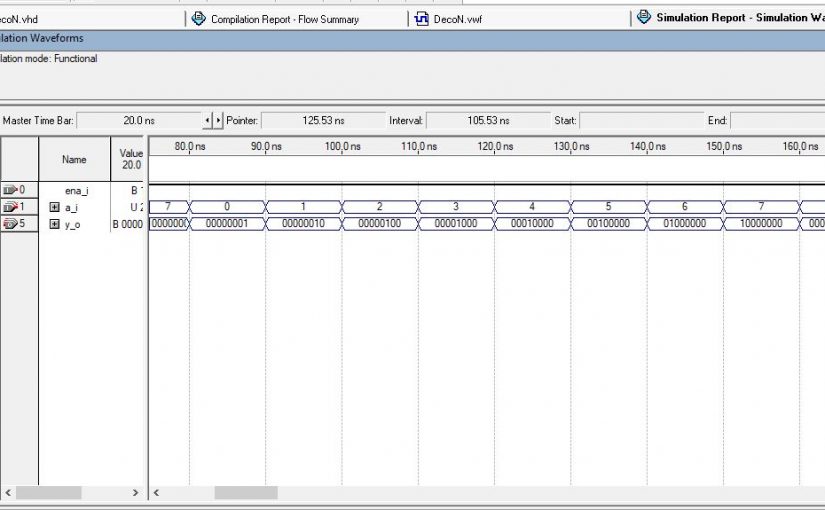

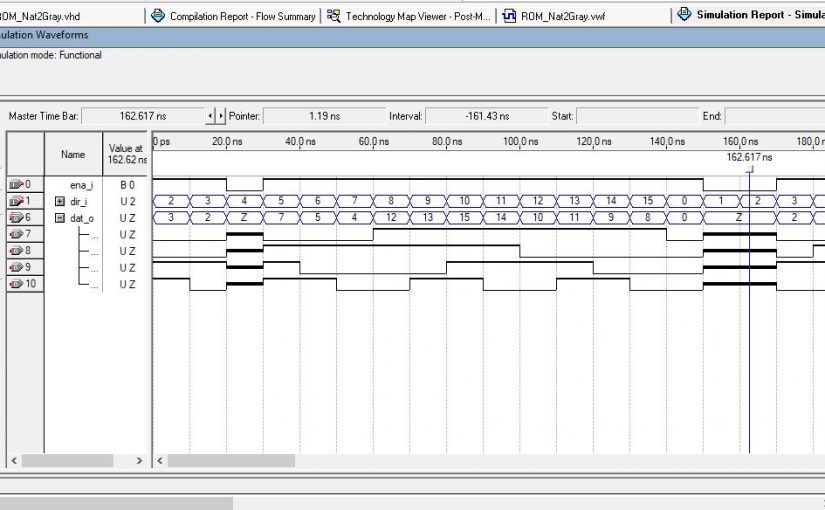

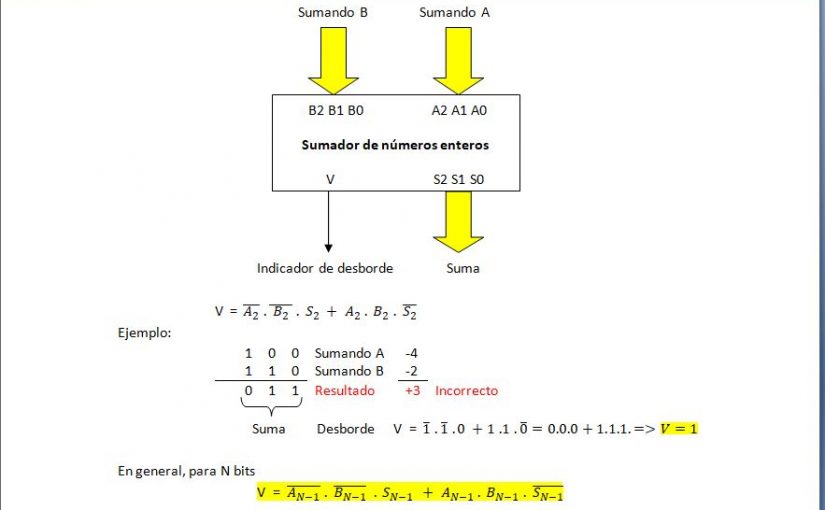

En este video analizo el RTL y el Technology Map Viewers comparándolos con la descripción VHDL y explicando que son los LE (Logic Element) y la LUT ( look-up-table) y cómo verlos en el Technology Map. Modifico la descripción eliminando una señal y muestro los efectos sobre el hardware sintetizado y los tiempos de propagación de las señales. Muestro las etapas del diseño CAD. Muestro como se asignan las patas. Explico la diferencia entre programar y configurar. Muestro cómo se usa el programador del Quartus II, para configurar la FPGA. Archivo de extensión SOF para bajar a la SRAM del Cyclone II.

Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

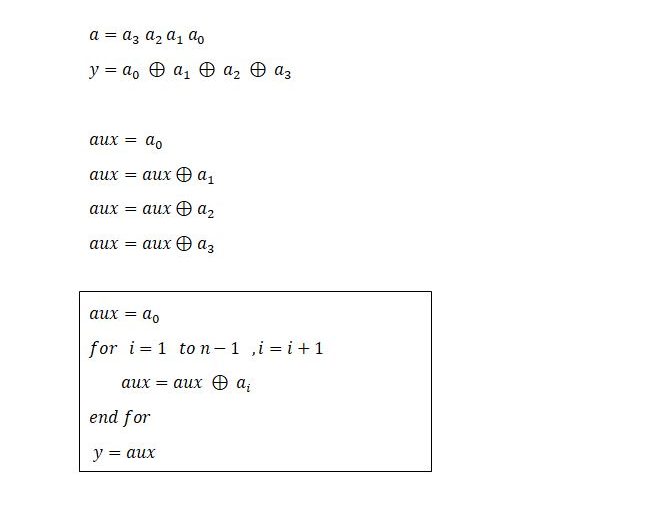

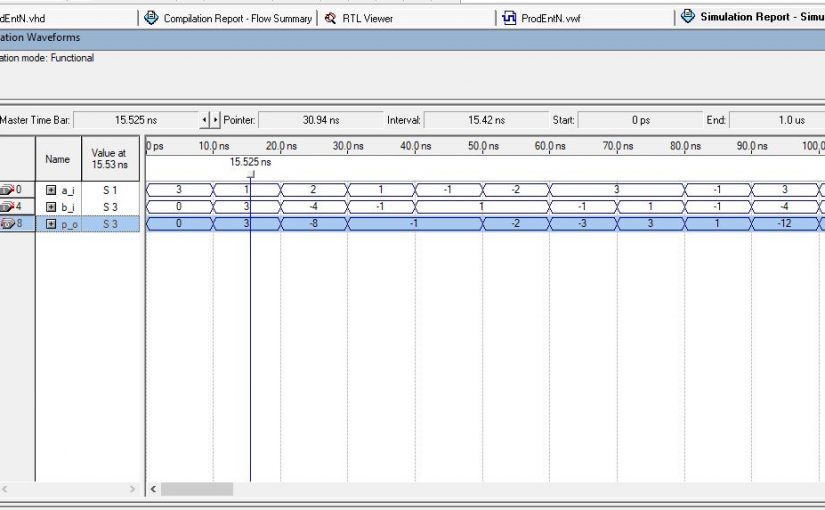

Análisis el RTL y el Technology Map Viewers