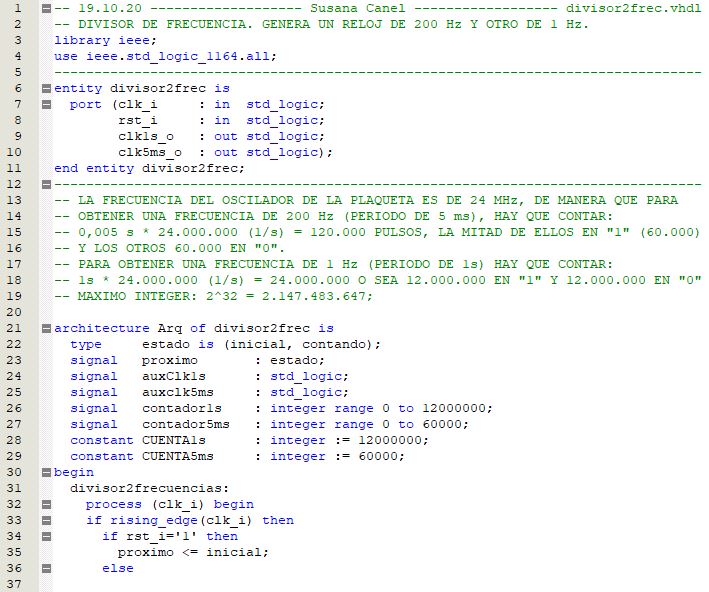

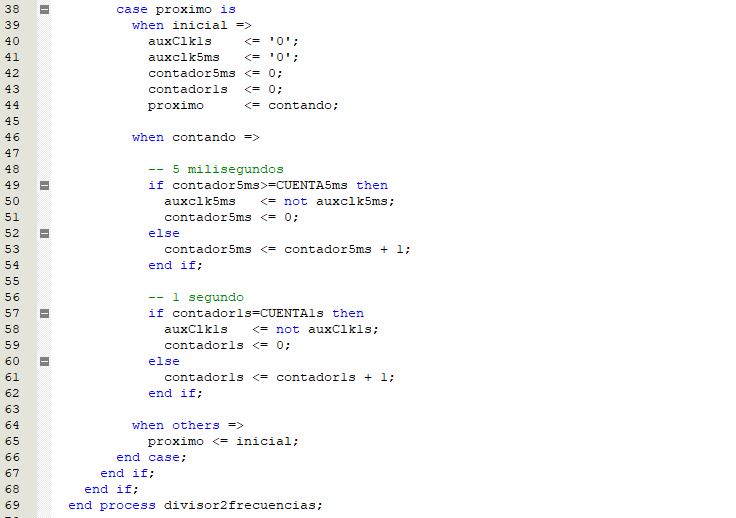

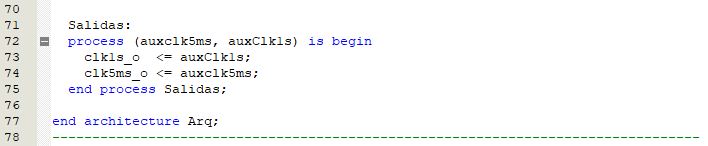

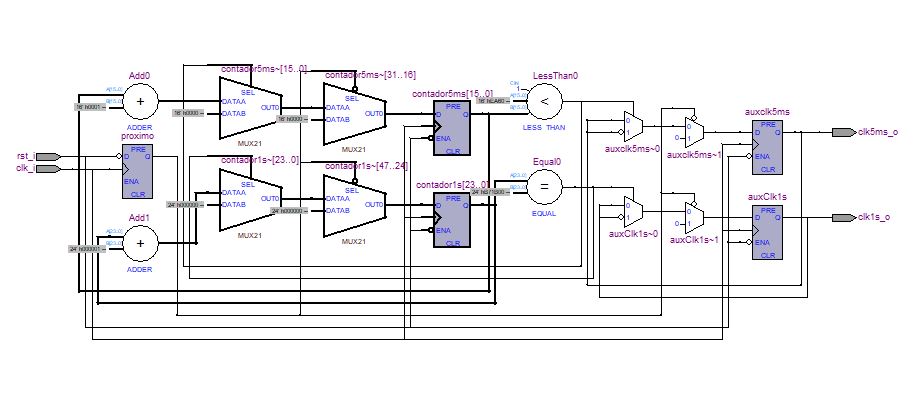

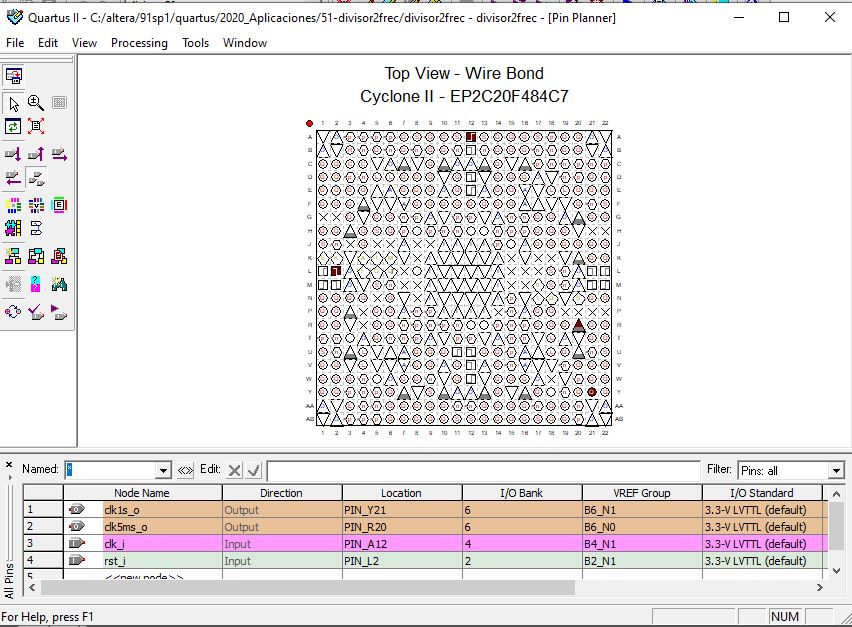

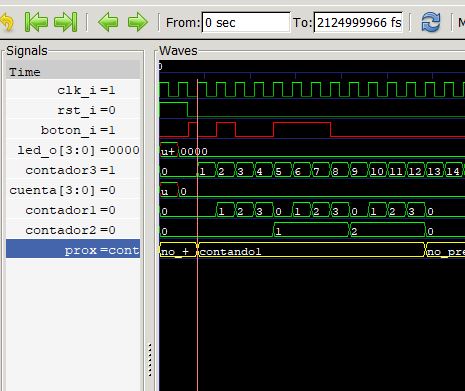

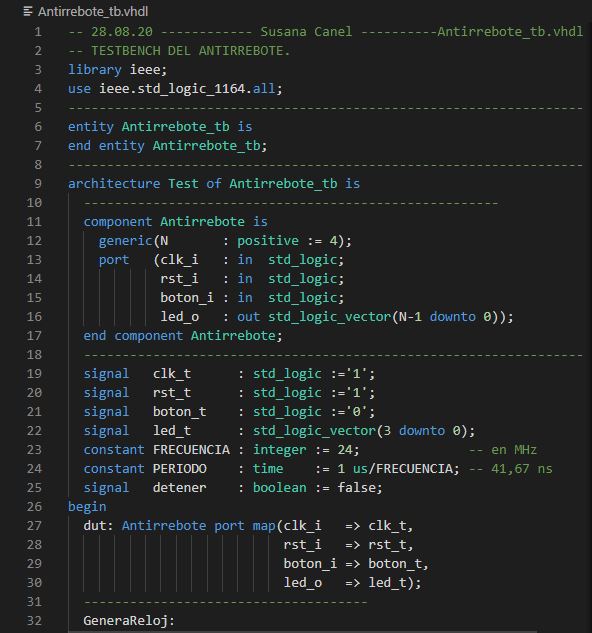

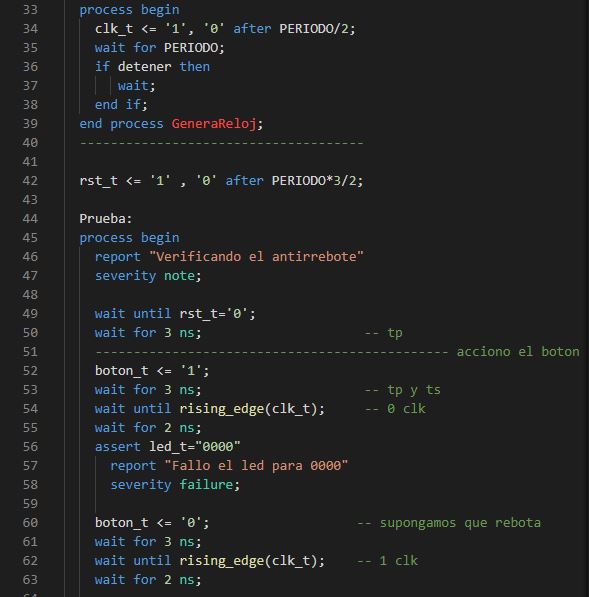

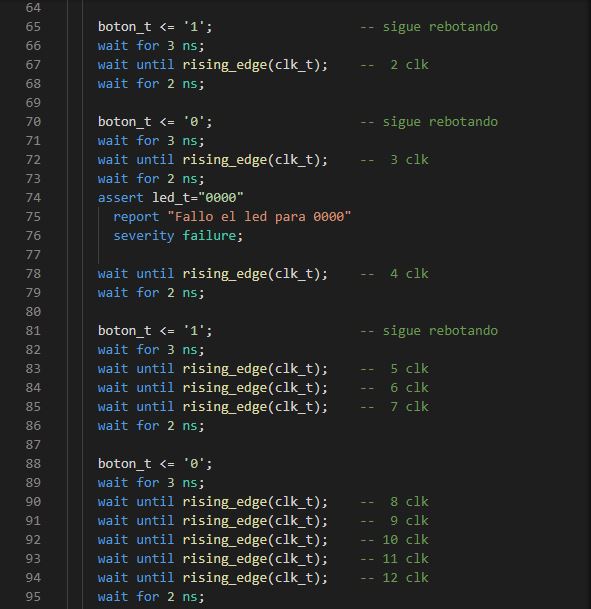

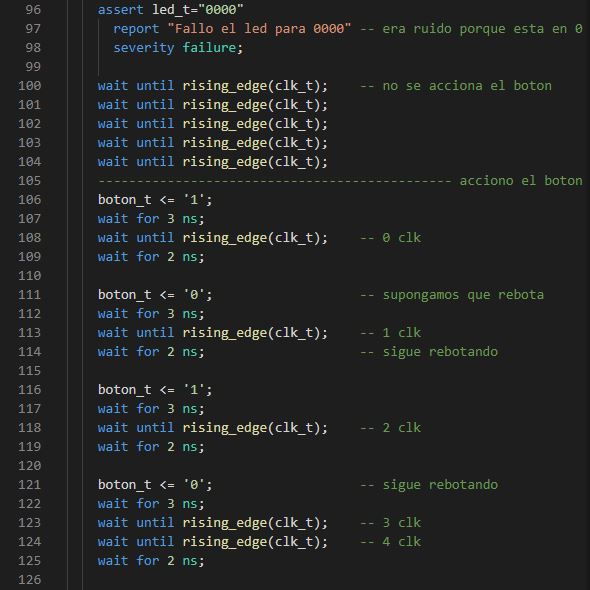

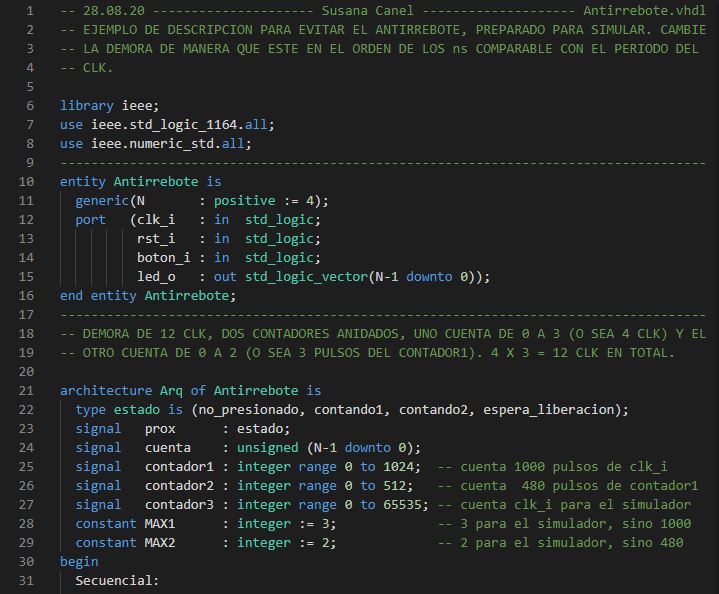

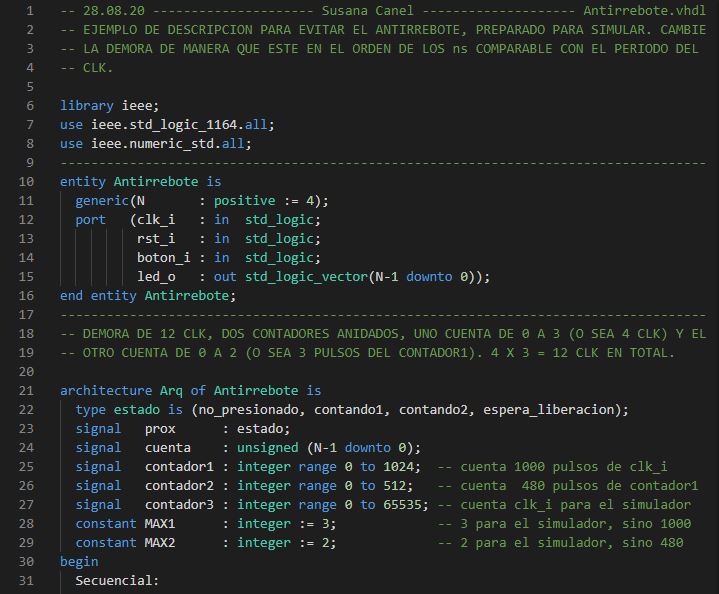

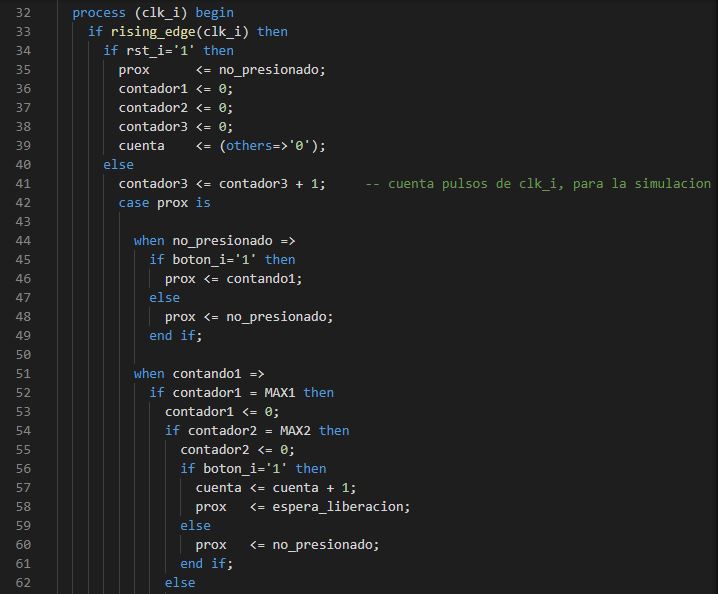

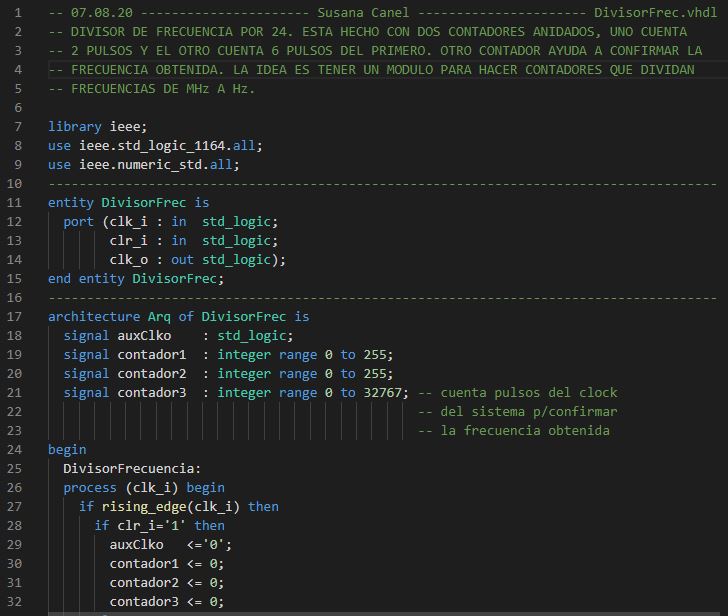

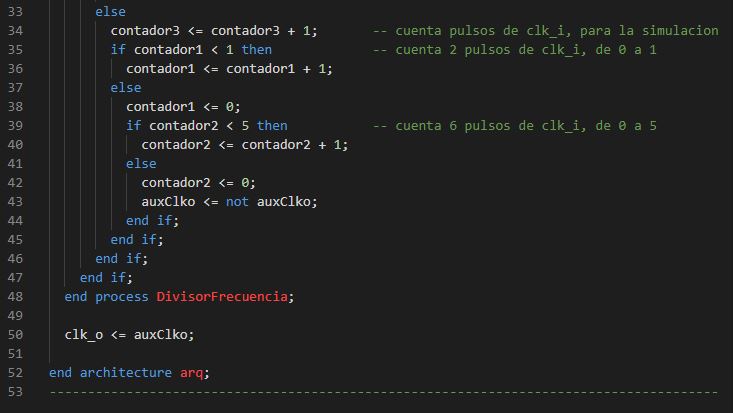

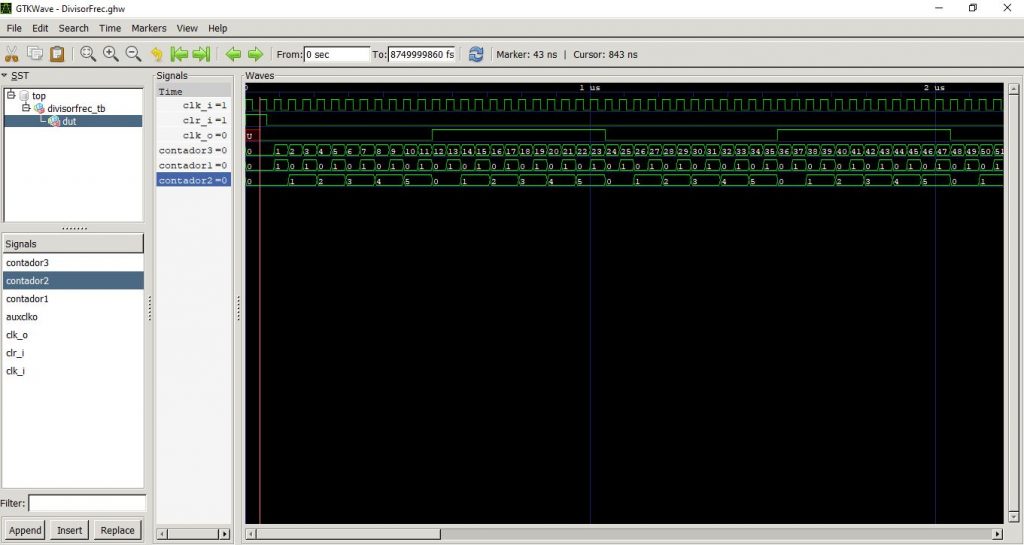

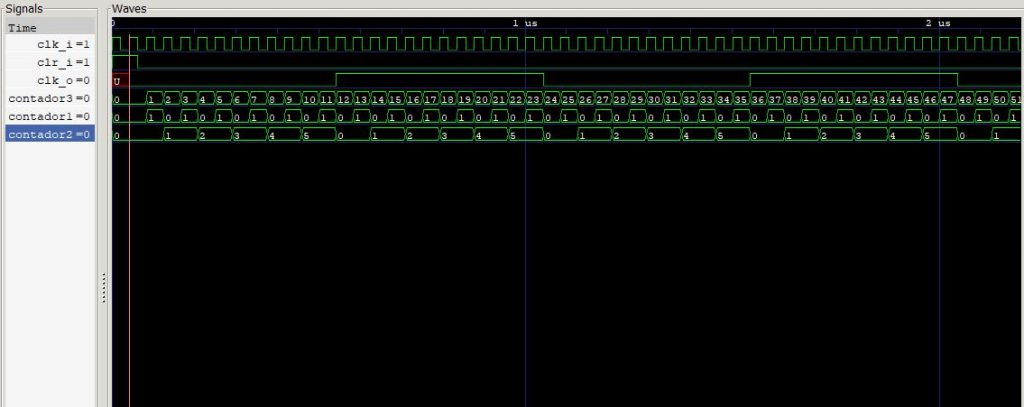

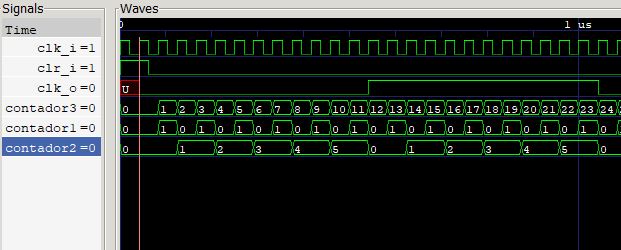

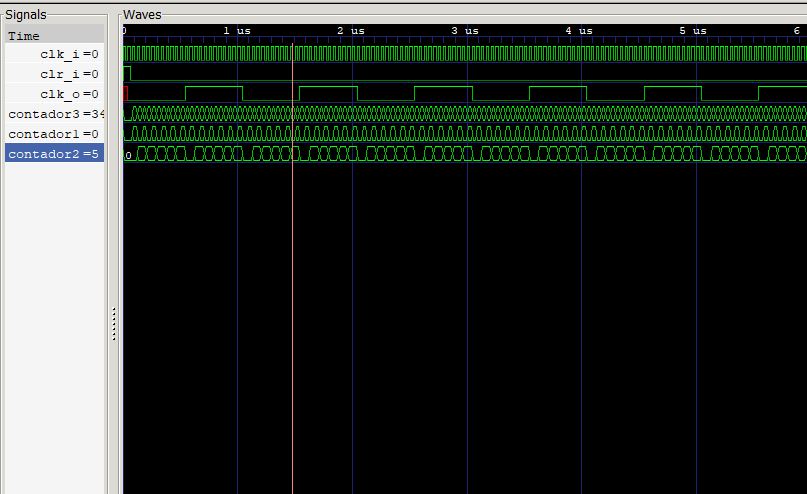

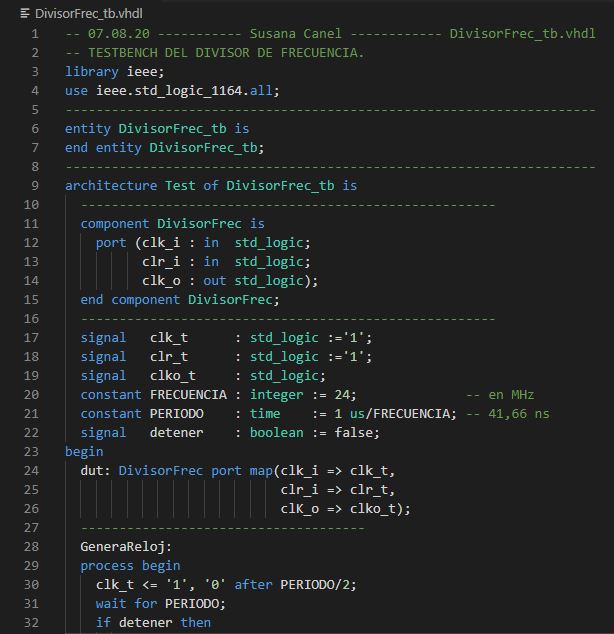

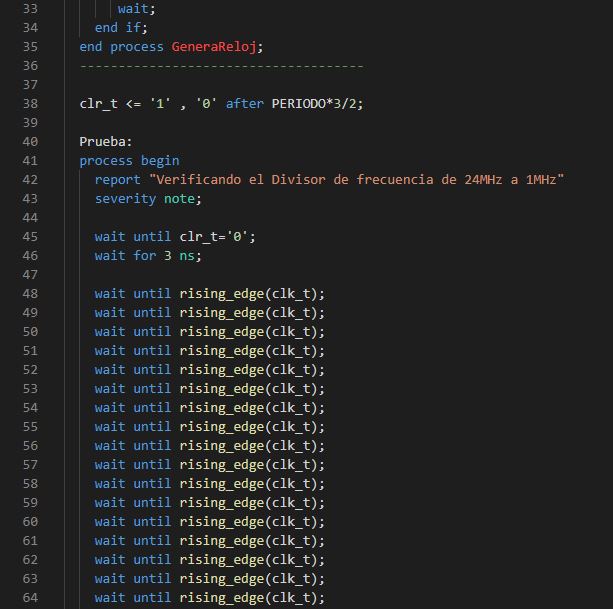

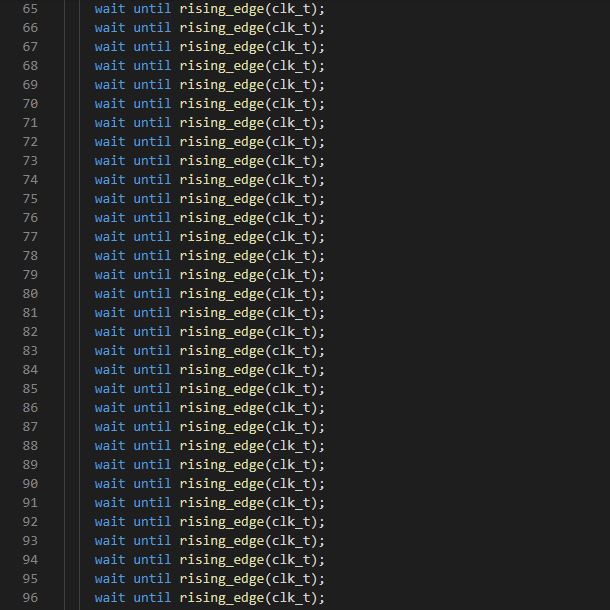

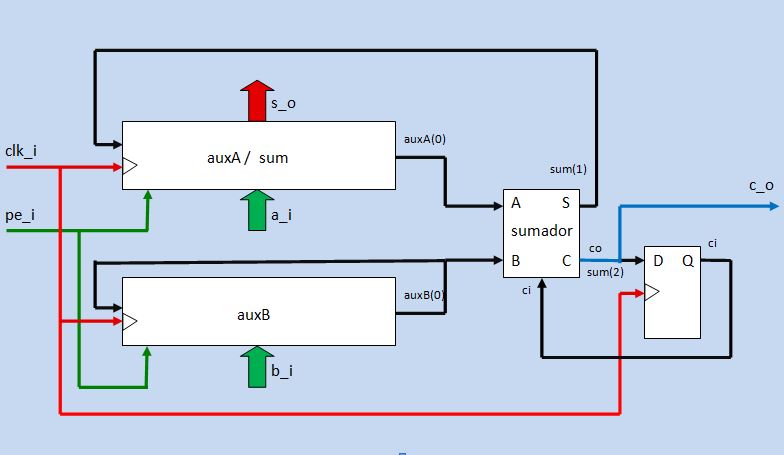

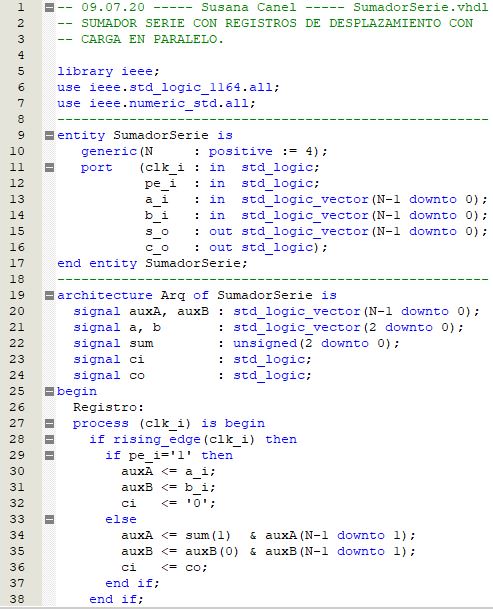

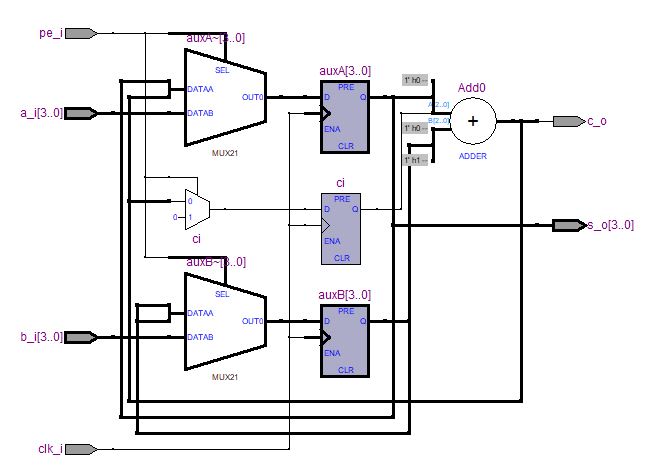

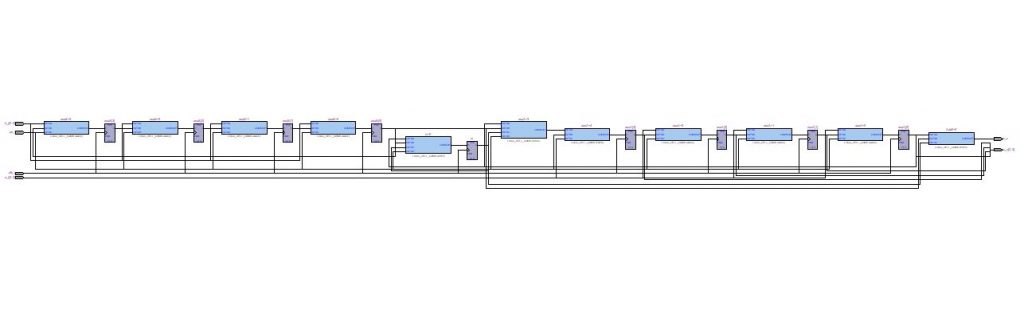

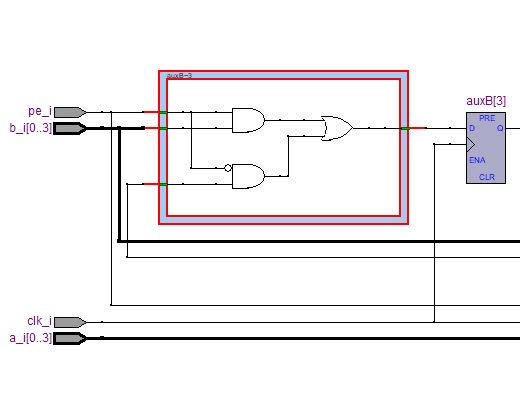

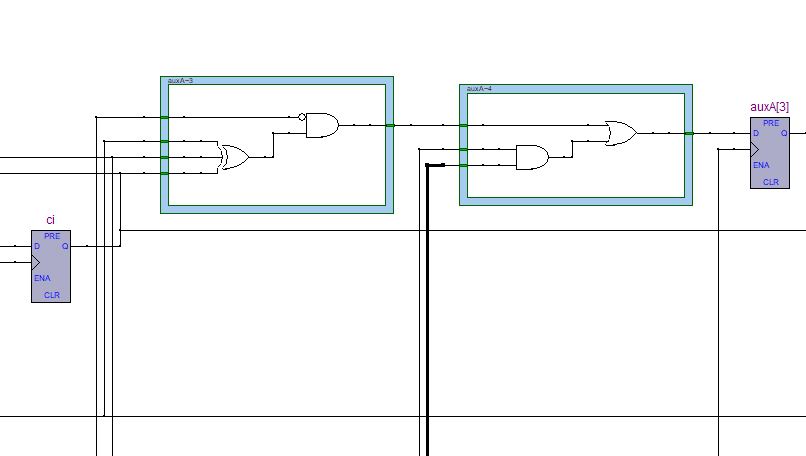

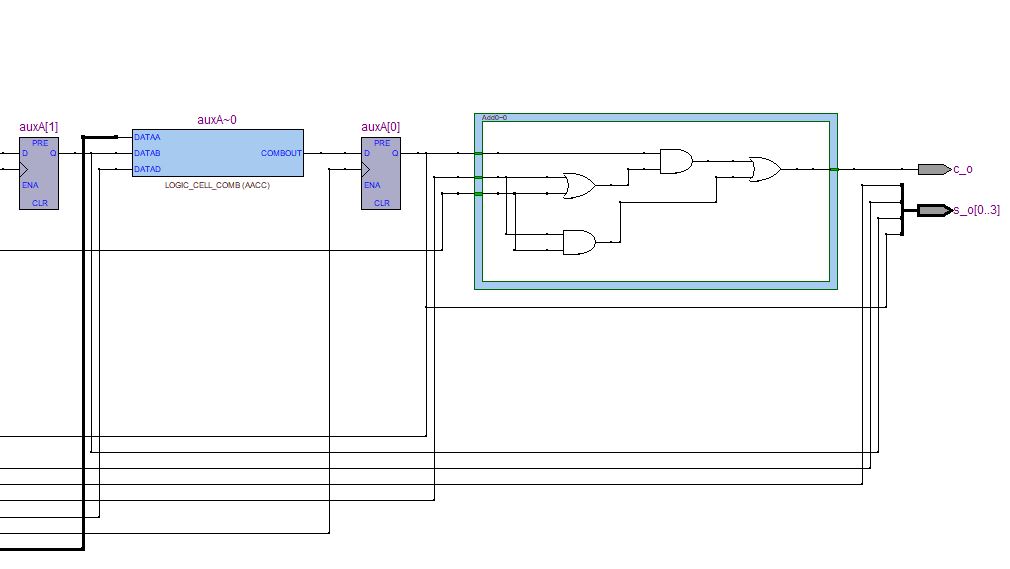

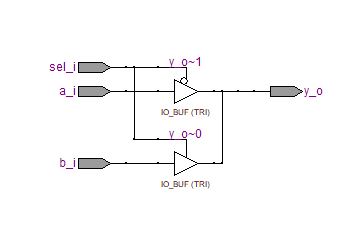

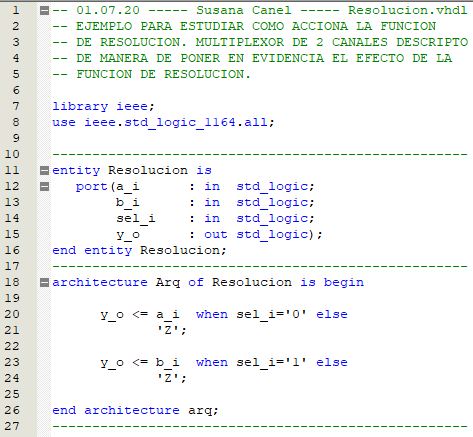

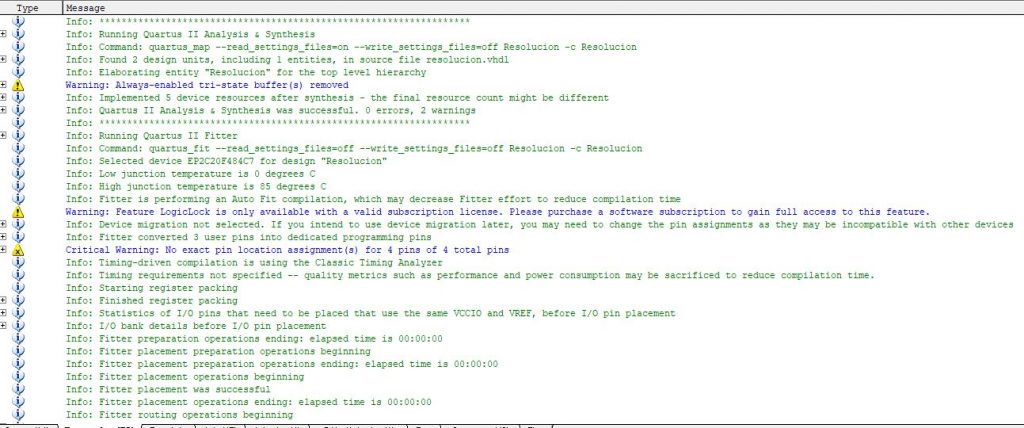

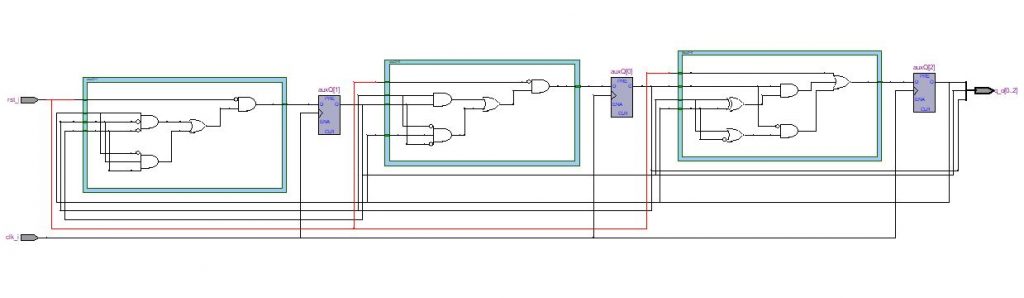

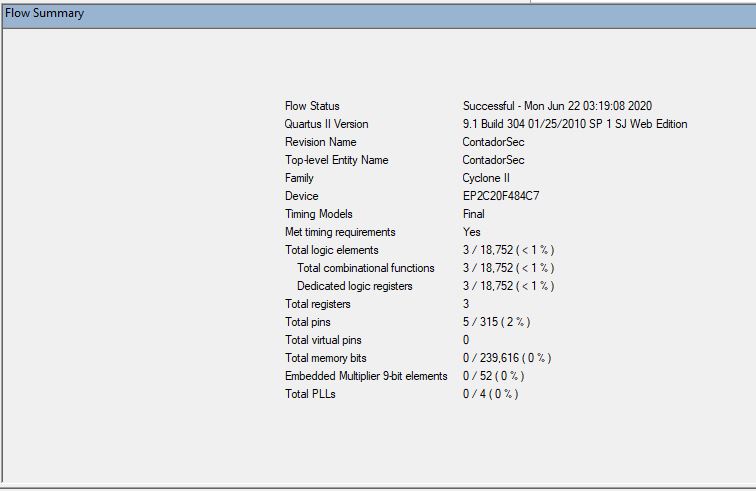

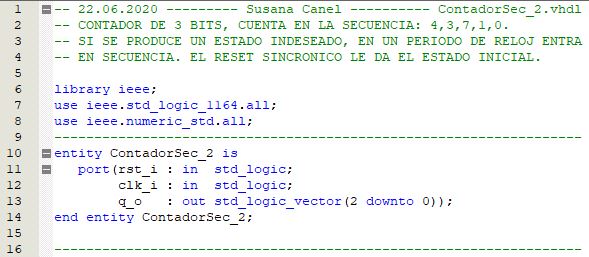

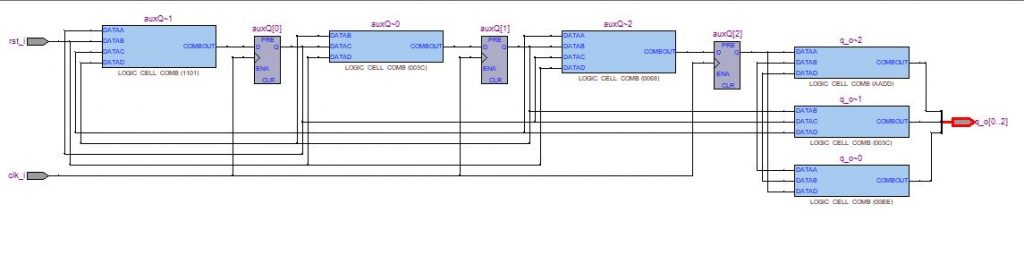

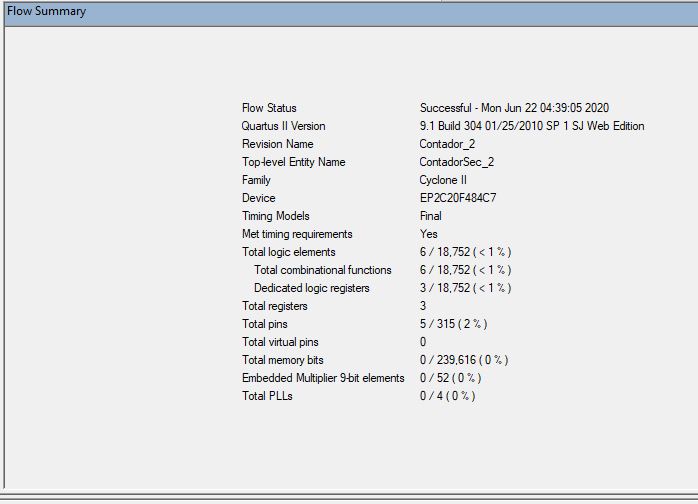

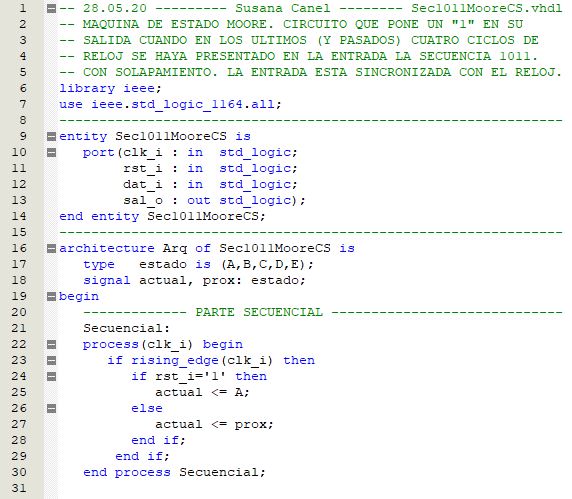

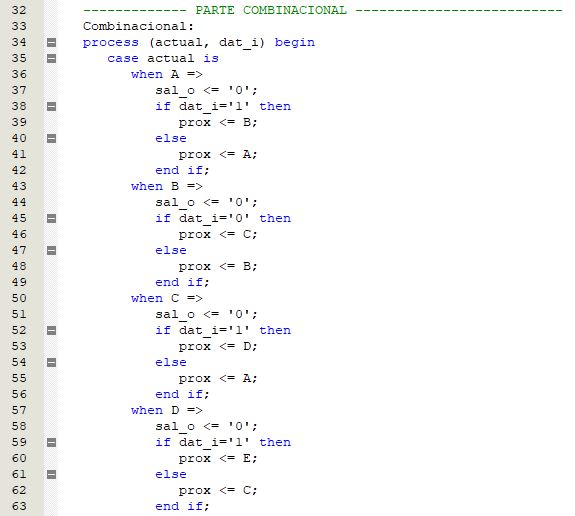

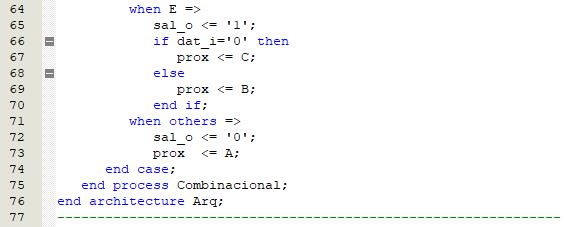

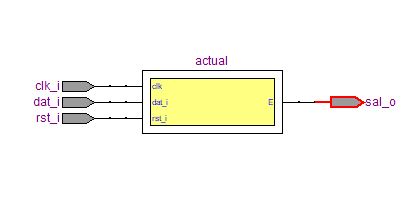

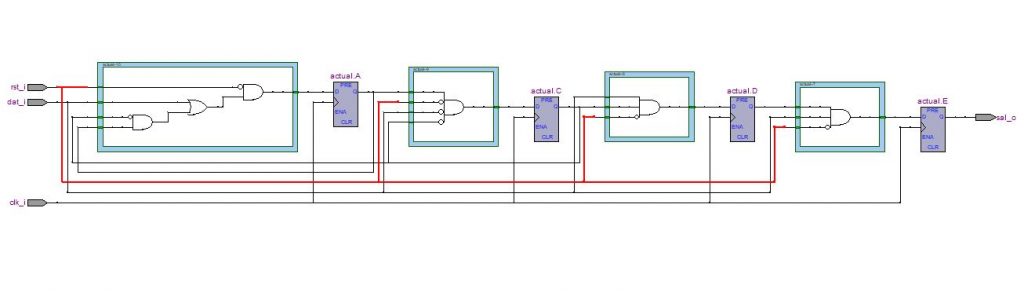

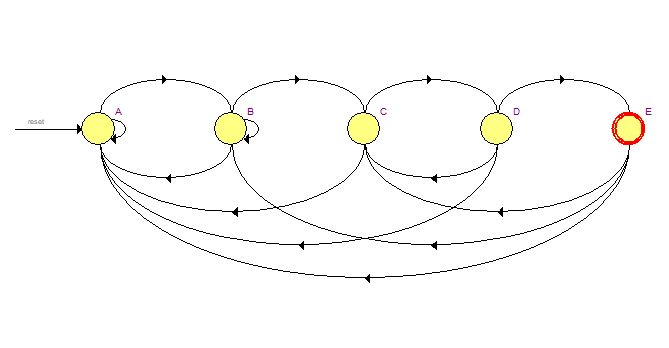

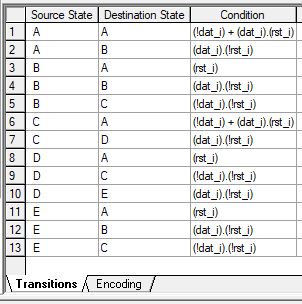

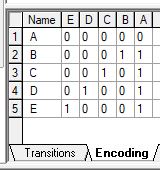

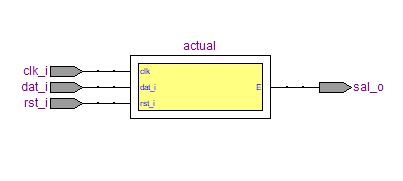

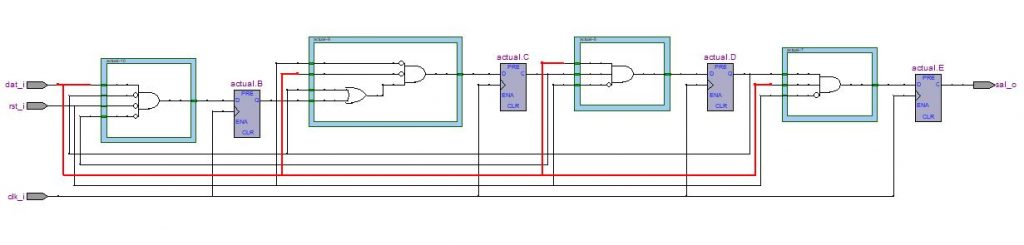

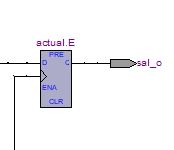

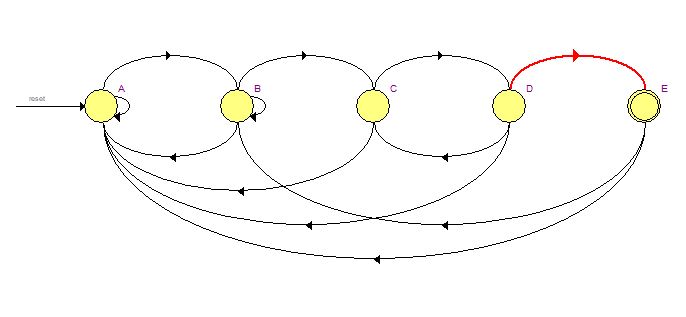

En este video te muestro cómo generar dos frecuencias distintas usando una sentencia “case”. Una frecuencia de 200 Hz, periodo de 5ms y otra de 1 Hz, periodo de 1 s, para usos generales. Te muestro el circuito esquemático generado por Nestlist Viewer de la herramienta Tool del Quartus II. Analizo la cantidad de multiplexores y de flip-flop tipo D necesarios para sintetizar el circuito cuando se usa el atributo “range” al definir una señal como “integer” y la comparo con la cantidad necesaria cuando no se usa ese atributo. Luego programo la plaqueta DE1 de Altera-Intel para verificar el correcto funcionamiento.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entrá en /contactame/.

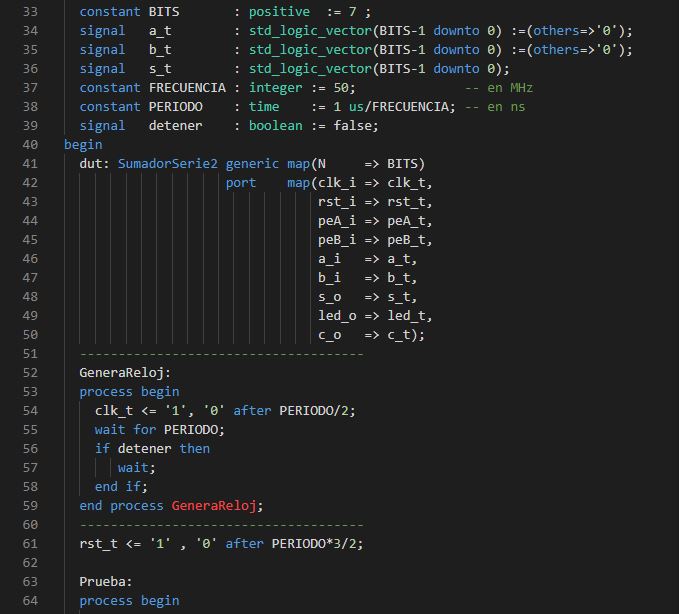

Puedes ver y descargar mis códigos fuente de: https://github.com/susanacanel/proyectos-vhdl.