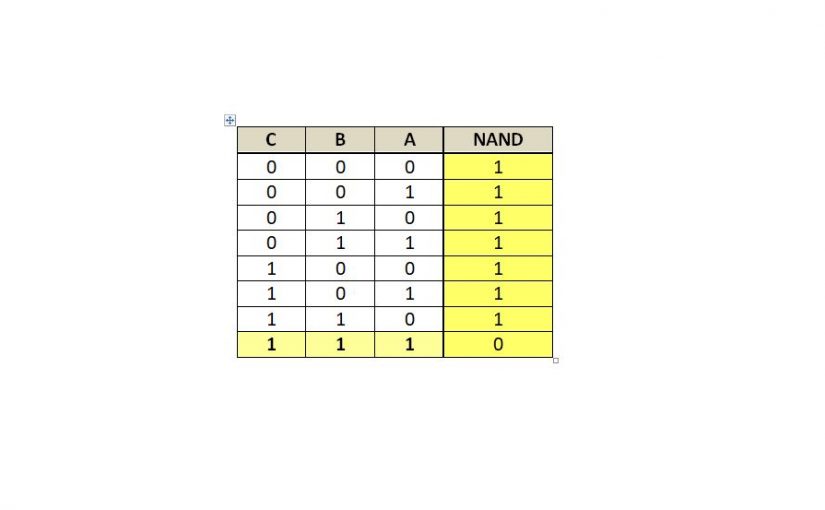

Puedes ver el código en mi post Lección 4. VHDL descripción algorítmica. /2018/09/03/leccion-4-arquitectura-algoritmica/ . A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/