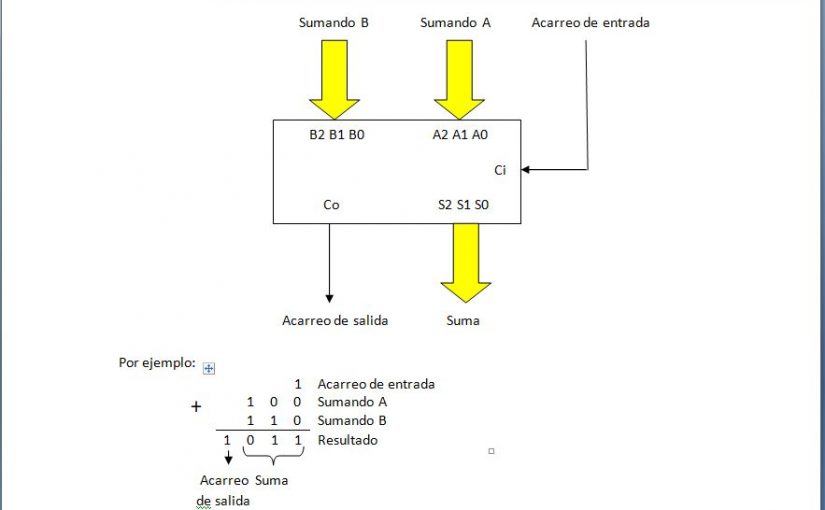

Descripción y simulación de un sumador binario genérico de magnitudes de N bits. Uso el package numeric_std para cambiar el tipo de datos a unsigned para así de poder realizar la suma. Recuerdo que no existe el casting de un std_logic a unsigned, hay que transformarlo en un std_logic_vector de un solo elemento. Cambio el largo de un vector concatenándole un ‘0’ adelante. Puedes ver el código en mi post Lección 3. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Categoría: nivel inicial

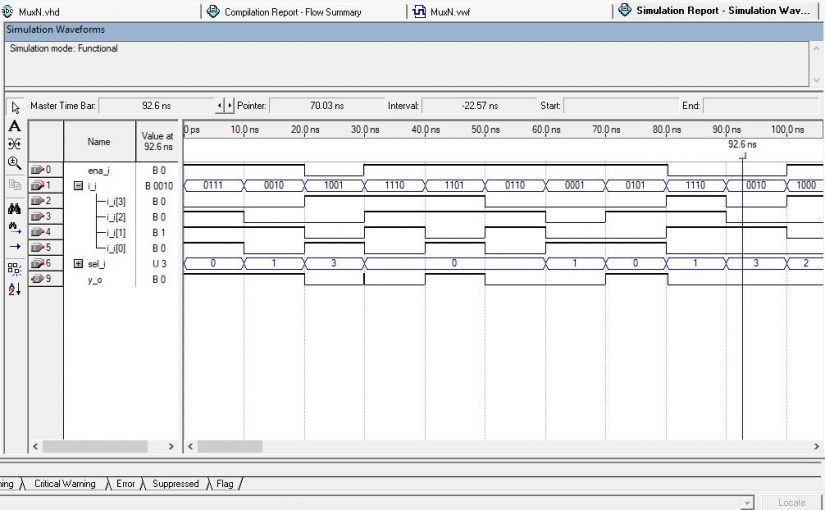

Lección 3.V15. Multiplexor genérico.

Descripción VHDL de un multiplexor genérico con entrada de habilitación activa en alto. Uso el package numeric_std para cambiar el tipo de datos de std_logic_vector a enteros (unsigned, to_integer). Uso Generic y constante de tipo positive (> 0). Luego de compilarlo sin errores, simulo el comportamiento. Puedes ver el código en mi post Lección 3. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

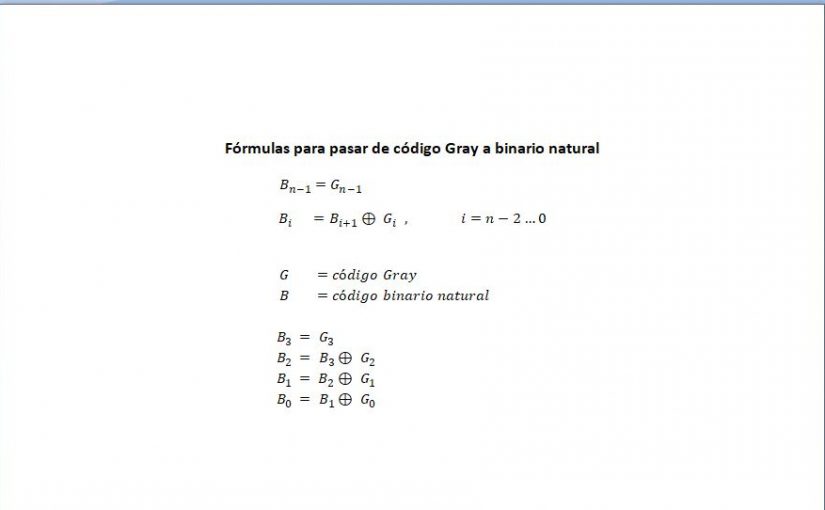

Lección 3.V14. Gray a binario, genérico.

Descripción VHDL de un conversor genérico de código Gray a binario natural de N bits. Uso generic. Uso la operación lógica xor entre vectores. Te muestro interesantes operaciones entre subíndices, que permiten resolver problemas en forma eficiente y compacta. Cometo adrede un error para destacar que las señales de salida no se pueden “leer” con esta norma. Compilo, veo cómo el software te informa de este error, lo corrijo, vuelvo a compilar y simulo. También te muestro cómo podés hacer consultas sobre la lista de operaciones lógicas y sintaxis en general acudiendo al insert template, el “papiro” del editor. Puedes ver el código en mi post Lección 3. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Lección 3.V13. Comparador genérico.

En este video te muestro la descripción de un comparador genérico de números enteros de N bits. En la entidad uso generic para darle un valor por omisión a la cantidad N de bits. Incluyo el package numeric_std porque necesito usar datos de tipo signed para realizar las comparaciones. Para finalizar realizo la simulación. Puedes ver el código en mi post Lección 3. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

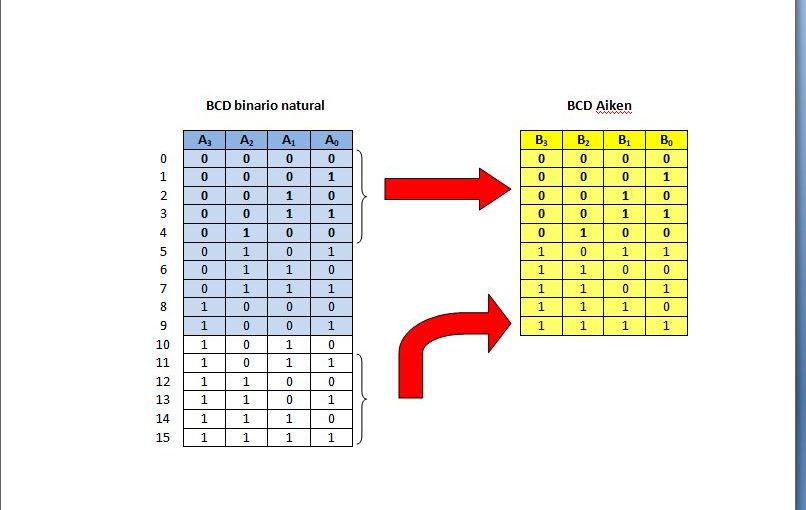

Lección 2.V12. BCD binario a Aiken.

En este video te describo un conversor de código BCD binario natural a código BCD Aiken, usando operaciones aritméticas que no están permitidas para el tipo de datos std_logic y std_logic_vector, motivo por el cual tengo que usar el package numeric_std del IEEE. Este package incluye nuevos tipos de datos, entre ellos unsigned. Haciendo conversión de datos soluciono el problema. Primero cometo adrede un error para que veas cómo te avisa el compilador que no puede hacer operaciones aritméticas con el tipo de datos std_logic_vector. Una vez corregido, lo vuelvo a compilar y finalmente simulo para comprobar el correcto comportamiento. También te muestro dónde se encuentran los package en la instalación de Altera, en particular los dos que hemos usado:

std_logic_1164 y numeric_std

Los abro para mostrarte parte del contenido, por ejemplo los tipos de datos que usamos en esta descripción. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

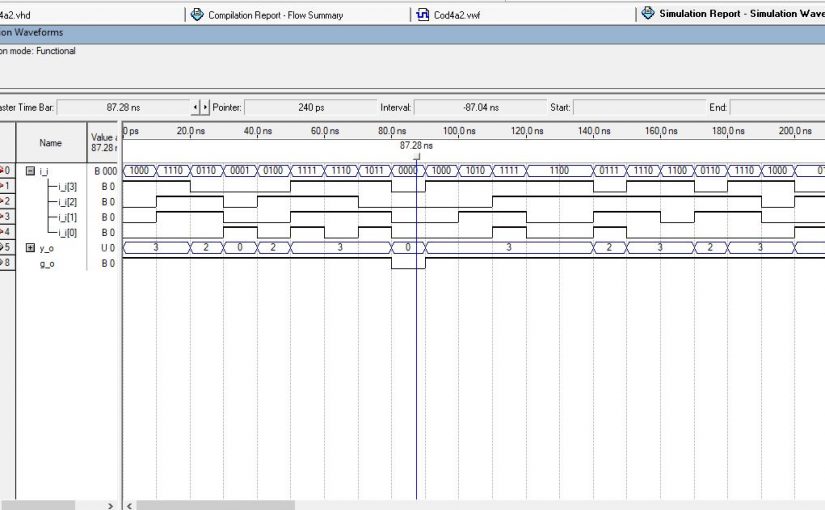

Lección 2.V11. Descripción y simulación de un codificador de prioridad de 4 vías.

En este video realizo la descripción VHDL de un codificador de prioridad de 4 vías con señal de grupo. Explico las características de la sentencia when-else que uso. Posteriormente realizo la simulación usando el Quartus II, 9.1. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

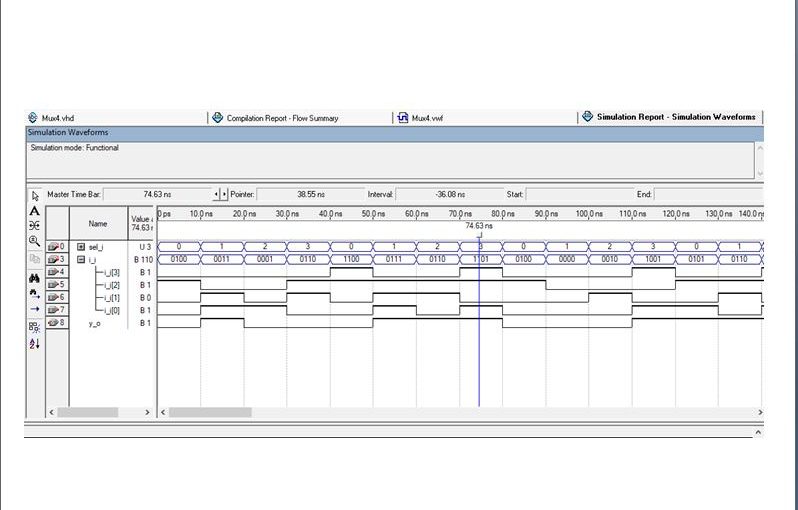

Lección 2.V10. Descripción y simulación de un multiplexor de 4 canales.

En este video te muestro la descripción de un multiplexor de 4 canales usando with-select para generar una tabla. Además adrede cometí un error en la descripción para mostrarte cómo lo informa el compilador. Posteriormente lo simulé usando el Quartus II, 9.1. y muestro cómo conviene elegir los estímulos de las señales. Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

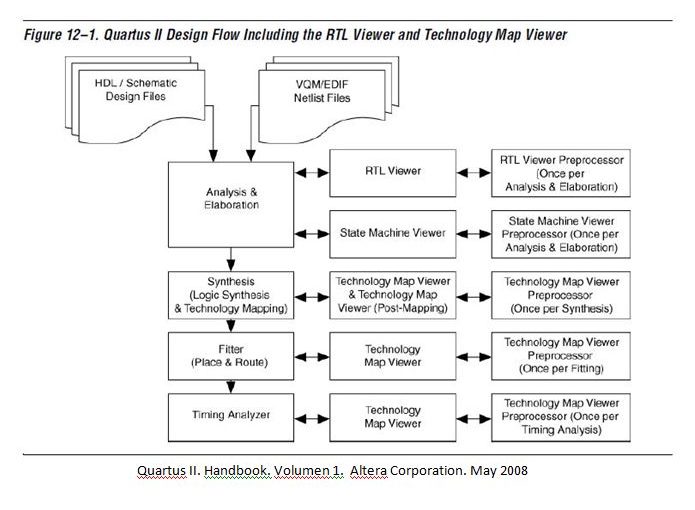

Lección 2.V9. Netlist Viewers del Quartus II: RTL Viewer y Technology Map Viewer

En este video te muestro los Netlist Viewers del Quartus II: RTL (Register Transfer Level), Technology Maps y Technology Maps (post-Mapping). Quién los genera, algunas caracterísiticas y usos.

Lección 2.V7. Descripción de un decodificador de 3 a 8 con habilitación.

Con este video inicio la Lección 2, que corresponde a descripciones VHDL de dispositivos combinacionales de propósitos generales o MSI. Describo un decodificador de 3 entradas a 8 salidas activas en alto, con entrada de habilitación también activa en alto. Uso las sentencias with-select para generar la tabla de verdad y las sentencias when else para poner la condición de habilitación. Uso when-others para cubrir todos los casos y la expresión (others =>’0′) para generar un std_logic_vector en 0 sin tener que conocer la dimensión del vector (el software ya posee esa información). Puedes ver el código en mi post Lección 2. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

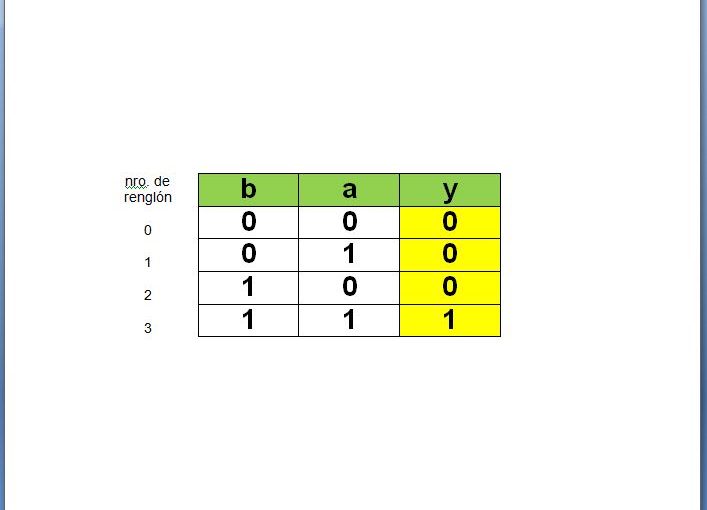

Lección 1.V6. Descripción de una tabla de verdad comprimida con punteros.

En este video te explico cómo describir una compuerta AND de 2 entradas con una tabla de verdad en forma comprimida mediante un puntero. Mantengo la entidad de los diseños anteriores, genero un vector con las dos entradas para lo cual las tengo que concatenar, como ya vimos en un ejemplo anterior. Y defino una “signal” de tipo “std_logic_vector”. Para hacer el “casting” incorporo un nuevo package: “numeric_std“. Defino una constante en la parte declarativa de la arquitectura y muestro cómo se hace un “casteo“. Puedes ver el código en mi post Lección 1. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/