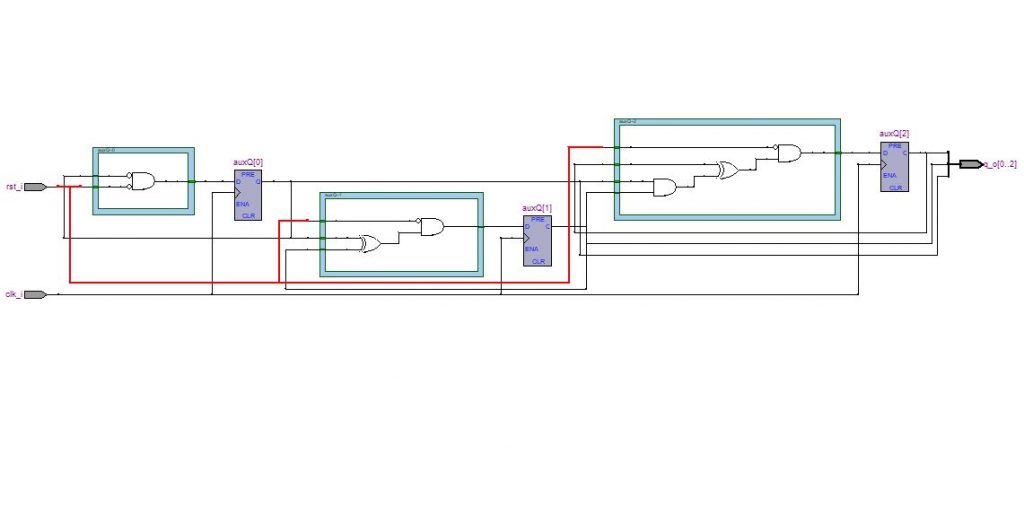

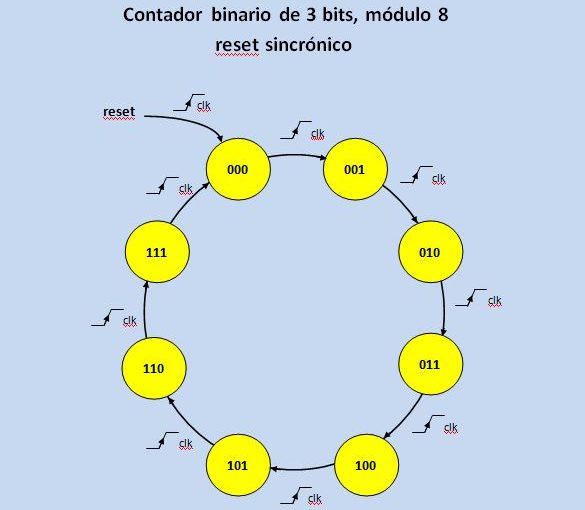

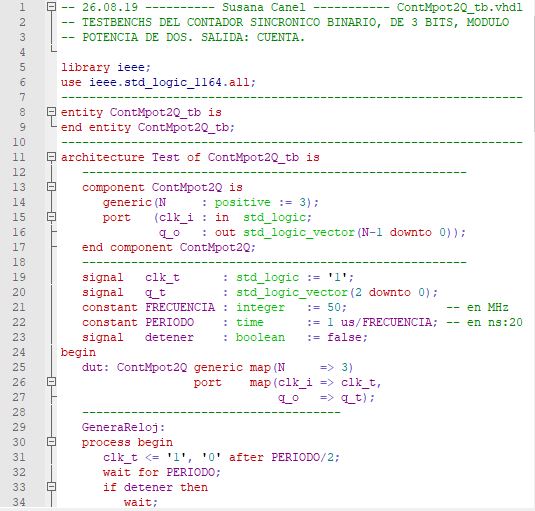

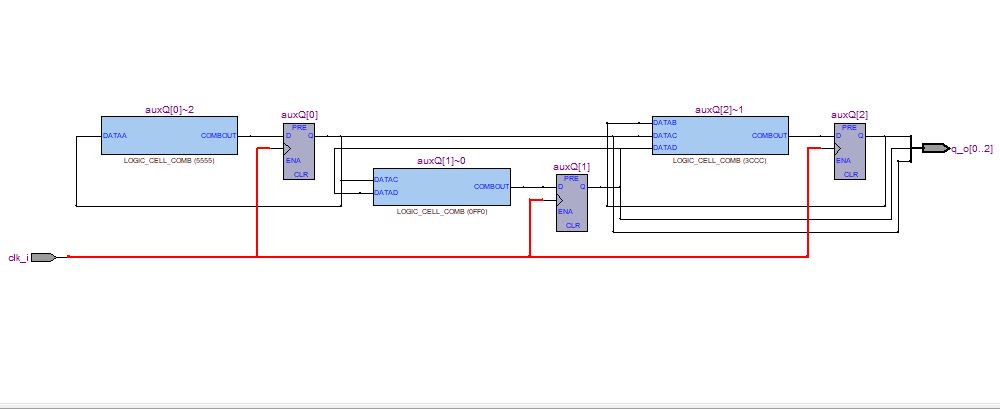

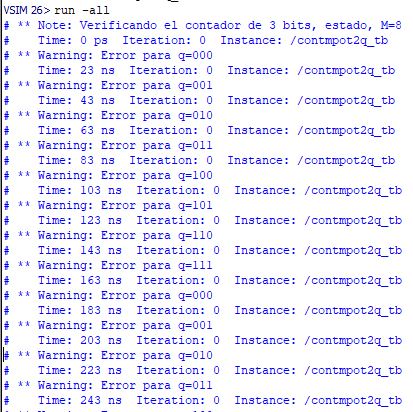

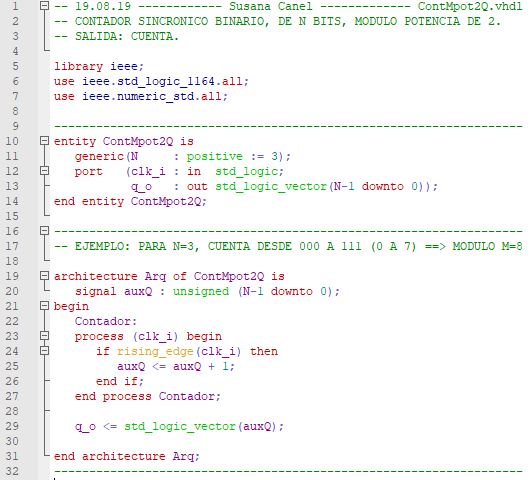

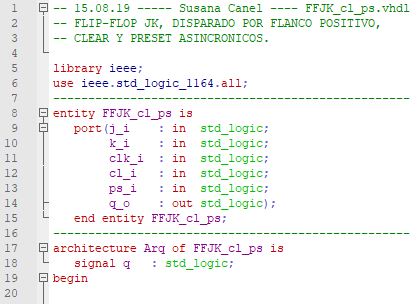

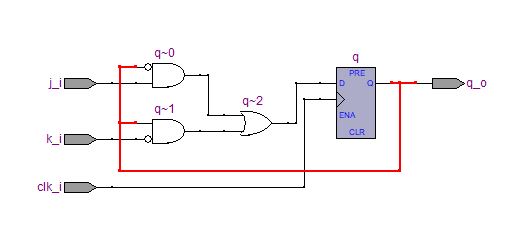

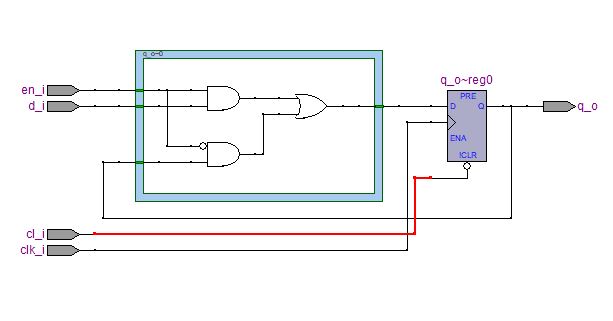

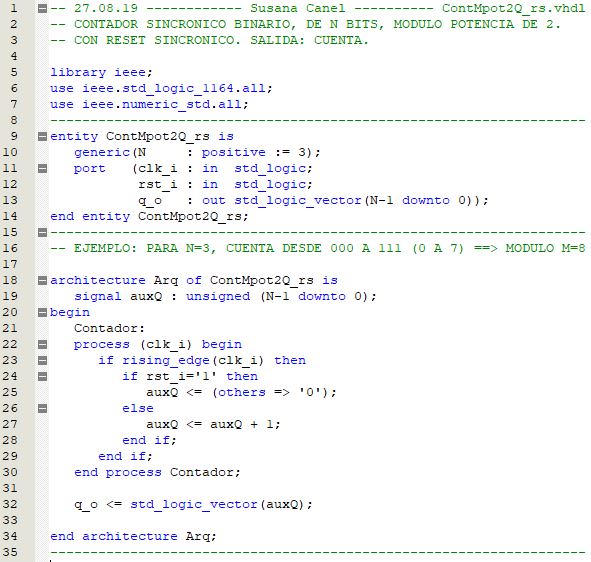

En este video te explico la descripción VHDL de un contador binario, genérico, de módulo potencia de 2, con reset sincrónico, también llamado cíclico. Tiene la entrada de pulsos a contar (reloj) y la de reset y como salida el estado de la cuenta. Como uso una señal de tipo unsigned incluyo el package numeric_std. Uso la función rising_edge. Compilo y controlo los “warnings”. Luego recurro a la herramienta “Tool” del Quartus II y selecciono “Technology Map Viewer” para ver y analizar el circuito esquemático generado.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/ .

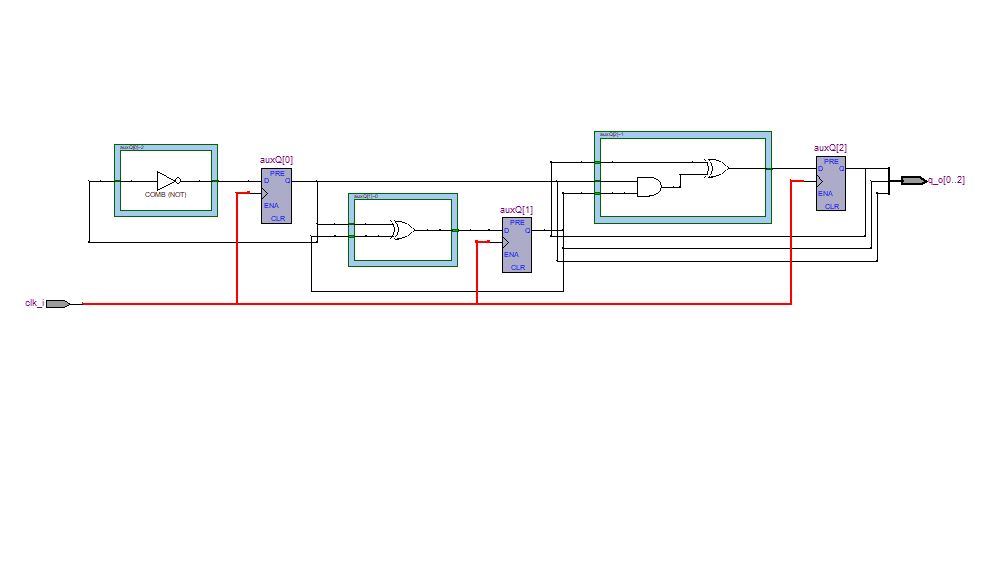

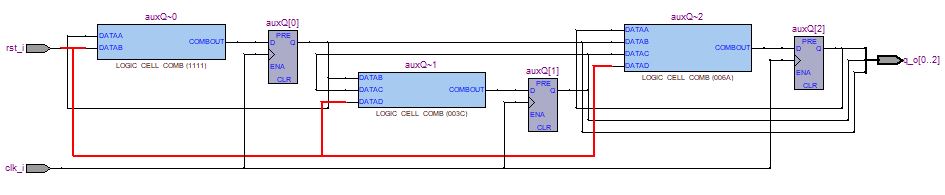

Desplegando el contenido de las celdas combinacionales vemos la señal de reset que llega a todas para generar en forma sincrónica el estado inicial del contador.