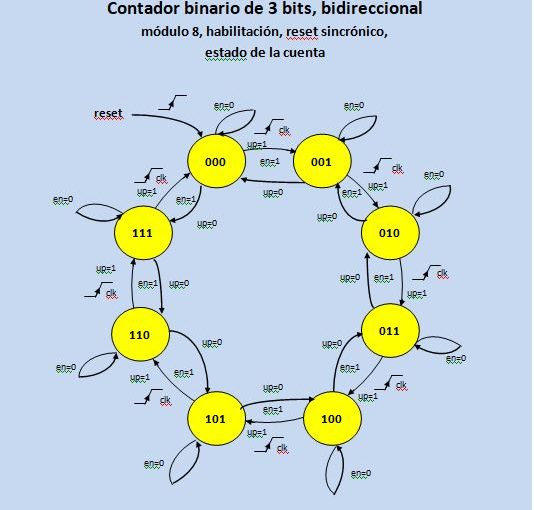

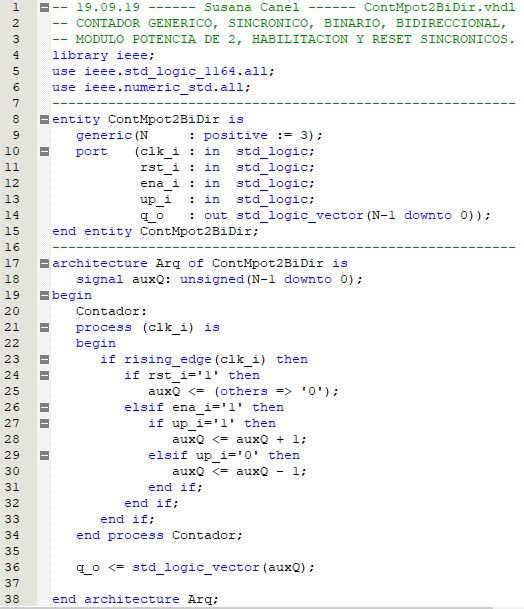

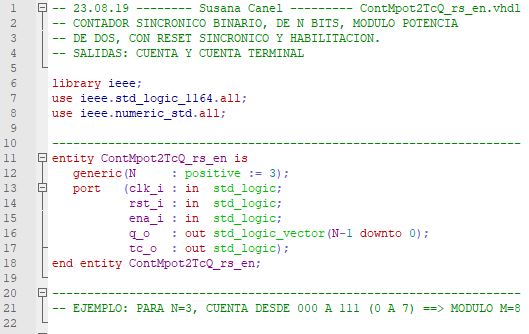

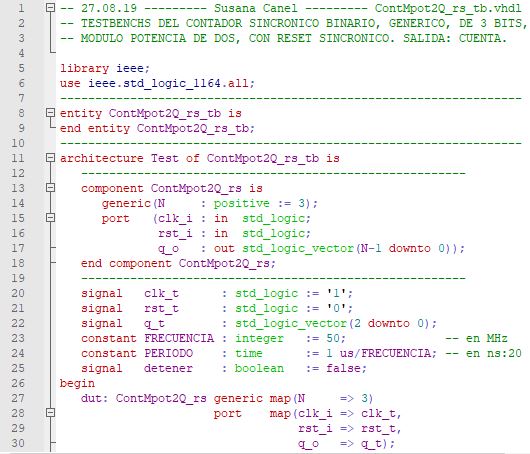

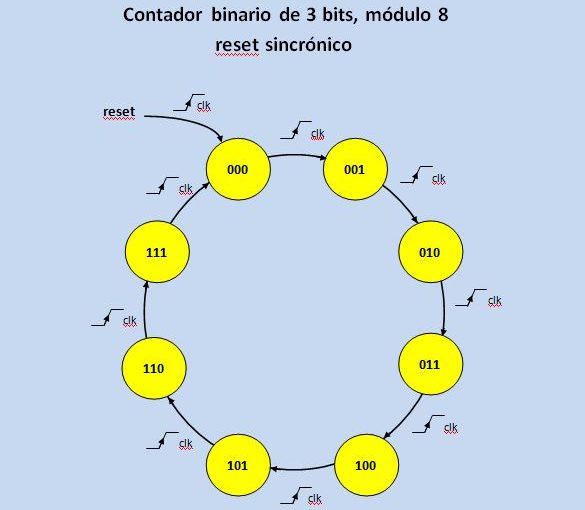

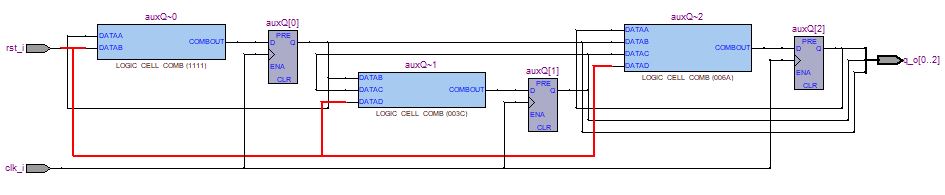

En este video te explico el testbench para el contador genérico, sincrónico, binario, con señales de habilitación y reset sincrónicos y con salidas: estado y cuenta terminal, descripto en el video anterior. El simulador produce el warning: METAVALUE DETECTED. Analizo este warning y explico cómo evitarlo.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entrá en /contactame/.

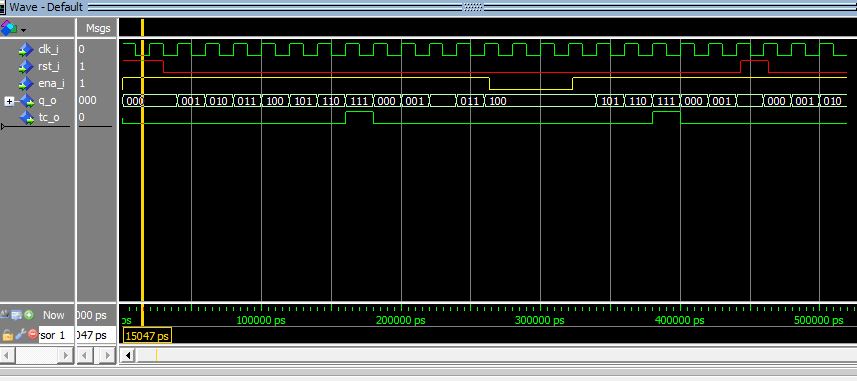

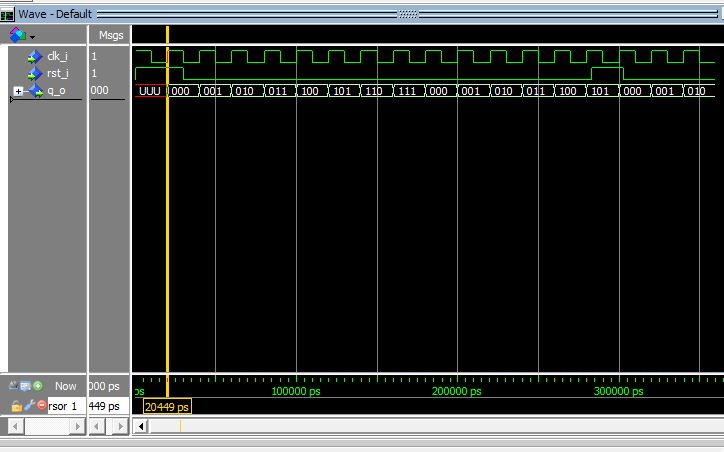

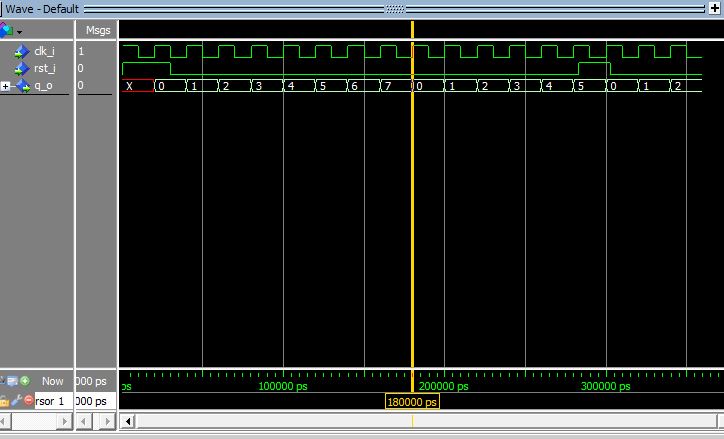

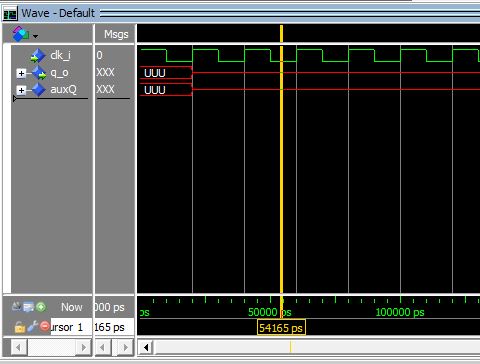

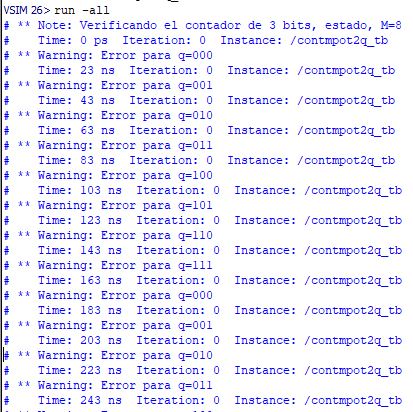

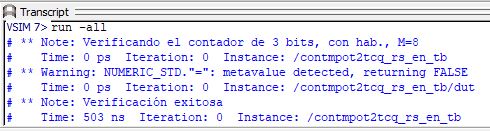

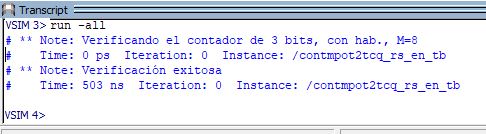

El ModelSim da el siguiente warning cuando simula:

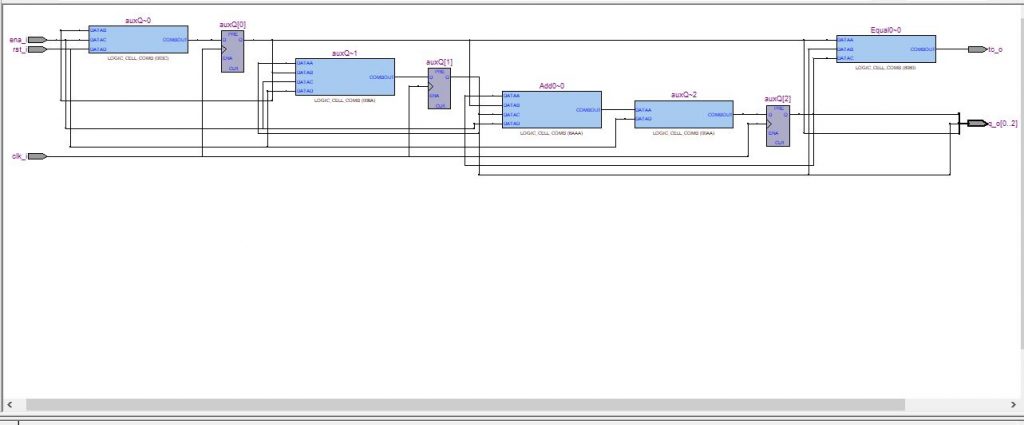

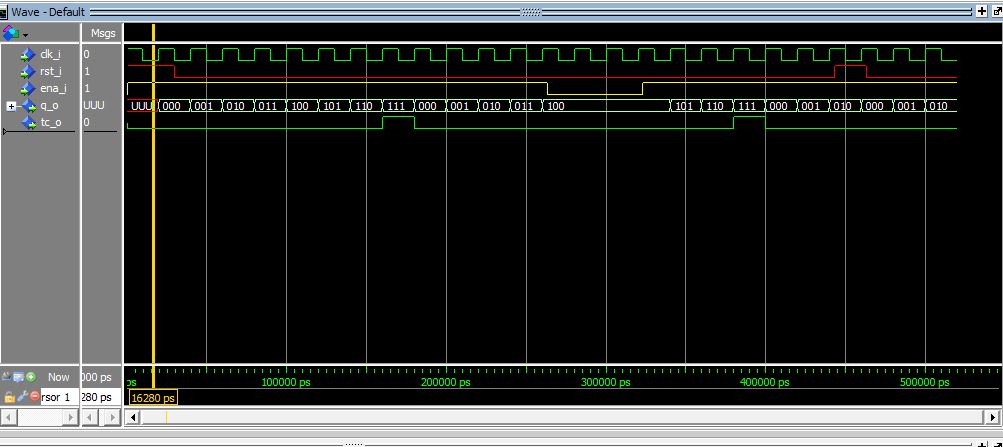

No obstante la decisión que tomó (FALSE) es correcta y vemos en la ventana de forma de ondas las salidas esperadas.

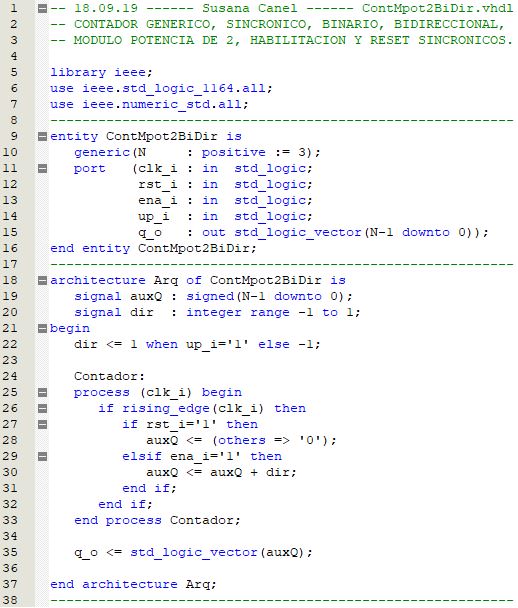

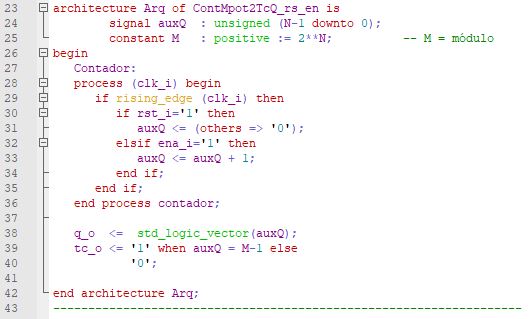

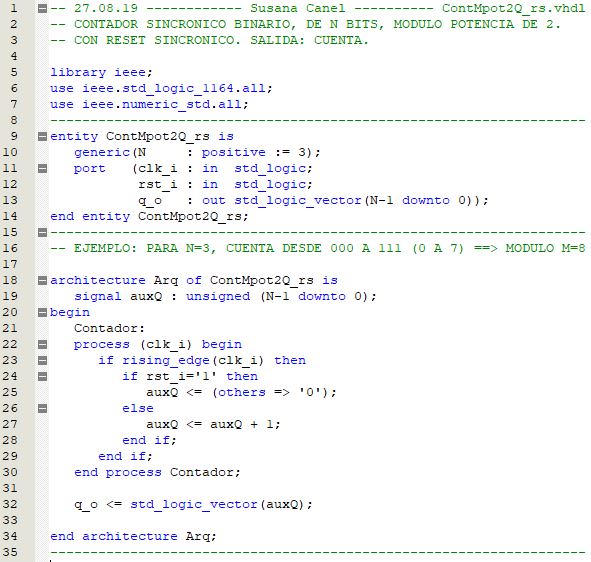

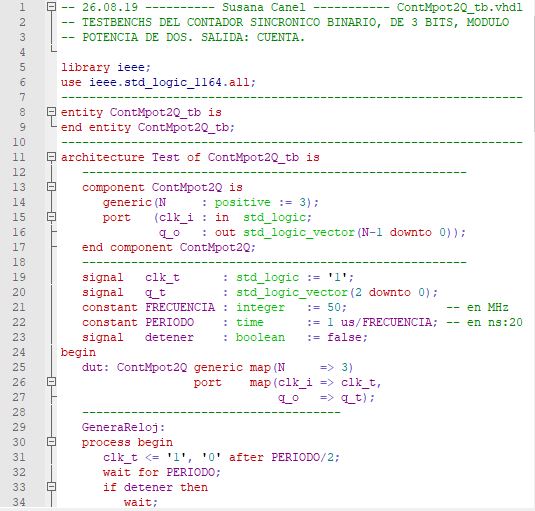

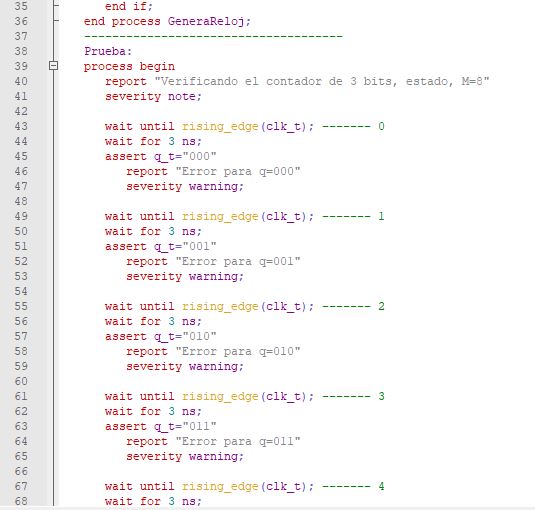

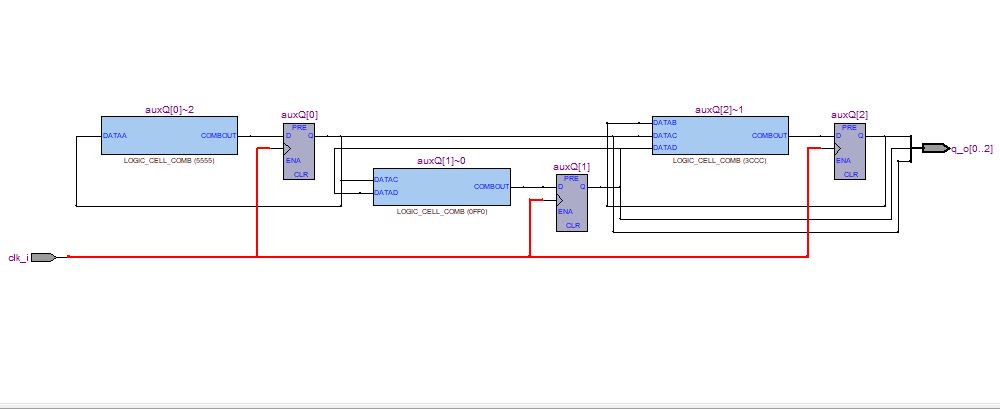

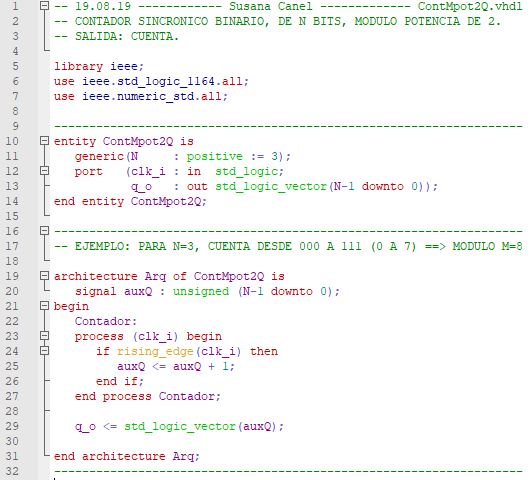

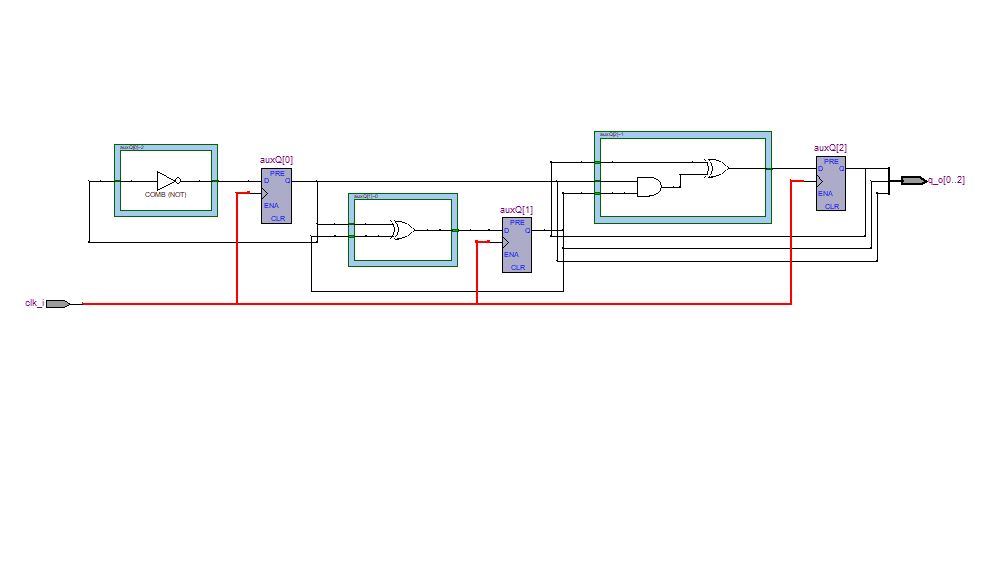

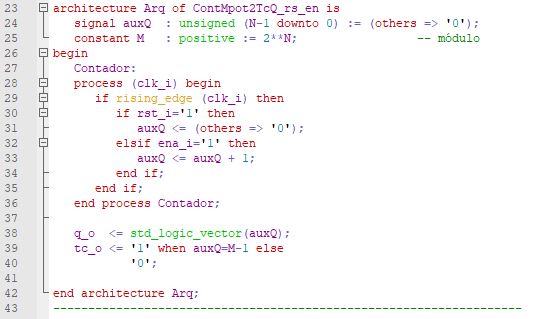

El warning es producido por la sentencia del renglón 39 de la descripción VHDL del contador, debido a que la señal auxQ no tiene un valor definido antes de que llegue el primer flanco creciente de la señal de reloj. El valor false que dio el simulador a la comparación: auxQ = M – 1, es correcto, por lo tanto tc_o tendrá un ‘0’ como valor inicial. Esto no es lo que sucede con el hardware, en el que ese valor no se puede conocer.

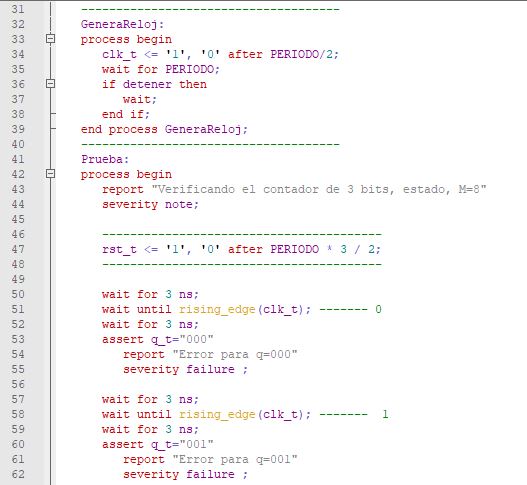

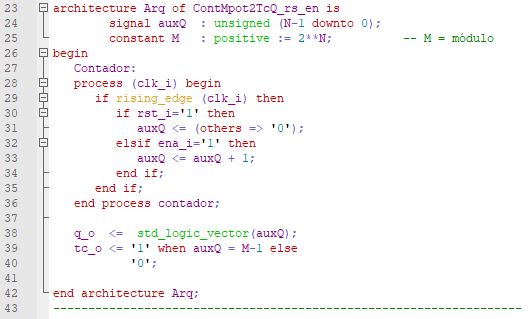

Hay una forma de evitar ese warning pero no es recomendable porque algunas FPGA sintetizarán hardware y otras no. Simplemente muestro cuál es pero no la voy a usar. Es mejor tener la información de este warning y estudiar a qué se debe y si para nuestro circuito es o no importante.

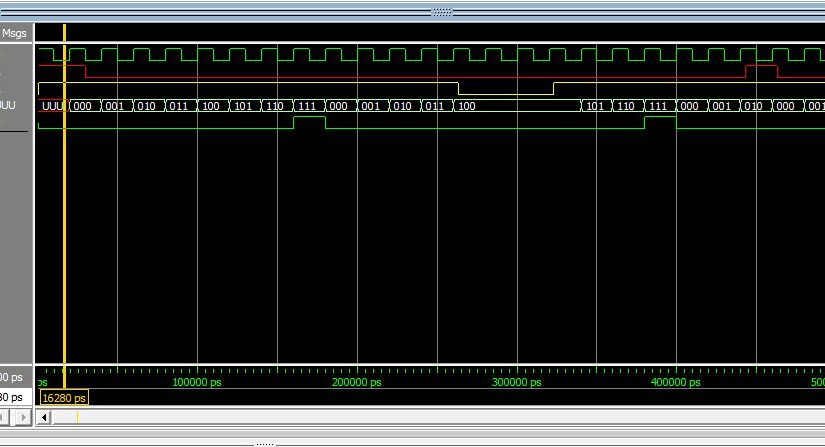

En el renglón 24, vemos la modificación, ahora la señal auxQ tiene un valor inicial. Para el simulador esta solución es óptima. No para todas las FPGA.

Cuando compilamos nuevamente con esta modificación y simulamos constatamos que el warning no aparece más en la ventana Transcript del ModelSim.

Vemos que en la ventana de forma de ondas ahora la salida q_o ya no tiene el símbolo ‘U’ de undefined, o sea, no inicializado. El resto está igual que en la anterior simulación.