En este video te muestro cómo modifiqué la descripción a fin de que no se encendiera el LED que indica que la suma es mayor que 9, cuando estoy en modo comparación. Recuerdo que los procesos implícitos son concurrentes. Explico que es importante elegir un adecuado lote de prueba tanto para verificar el correcto funcionamiento del hardware como del software cuando se escriben los programas llamados “testbench”.

Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Autor: Susana Canel

Lección 5.V25.3. Sintetizando el circuito en la plaqueta DE1 de Altera.

En este video muestro el efecto de ejecutar el circuito sintetizado en la FPGA Cyclone II de la plaqueta DE1 de Altera y manejando los interruptores, el display de 4 dígitos de 7 segmentos y un LED. Uso el modo de programación JTAG. Tengo instalado el driver USB-Blaster de Altera.

Para los que usan la plaqueta, hay un interruptor RUN/PROG, que cuando se usa el modo JTAG tiene que estar en la posición RUN.

Imparto el curso VHDL de nivel inicial completo (o sea incluyendo dispositivos secuenciales) y con prácticas sobre la plaqueta DE1, en Buenos Aires.

Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

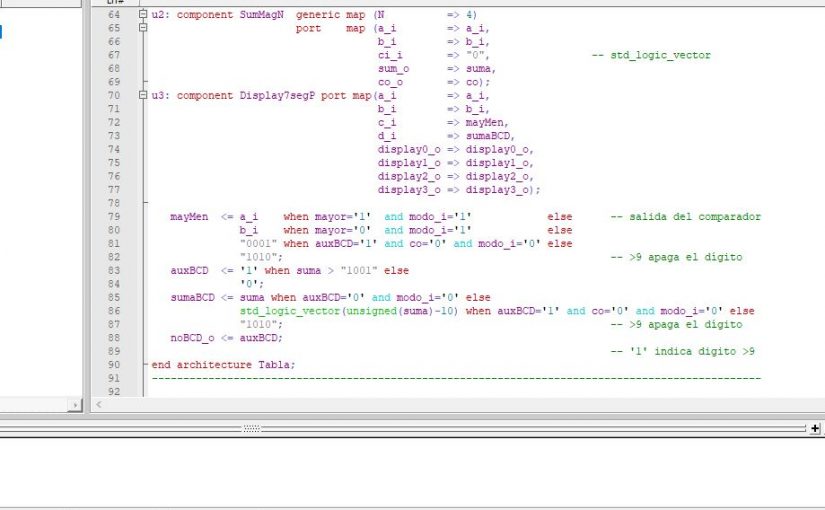

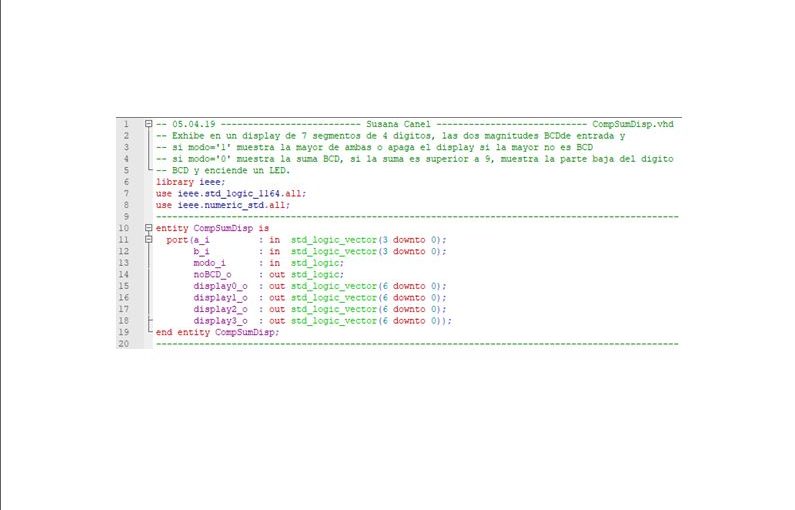

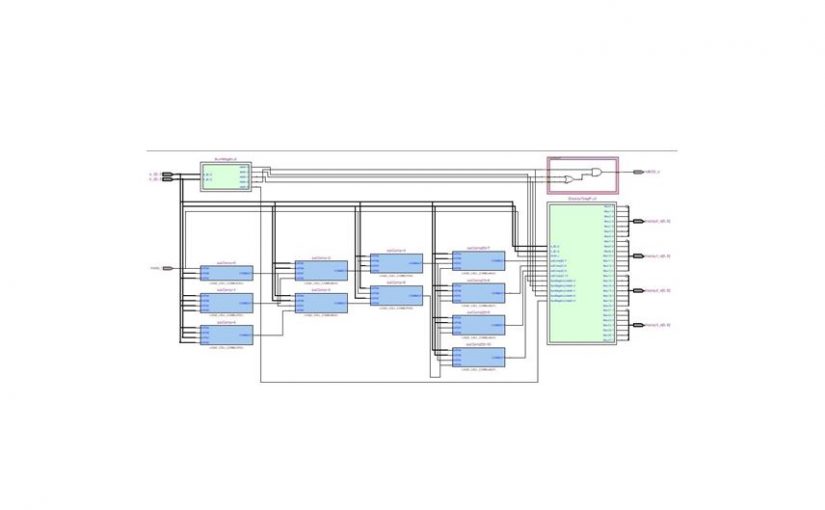

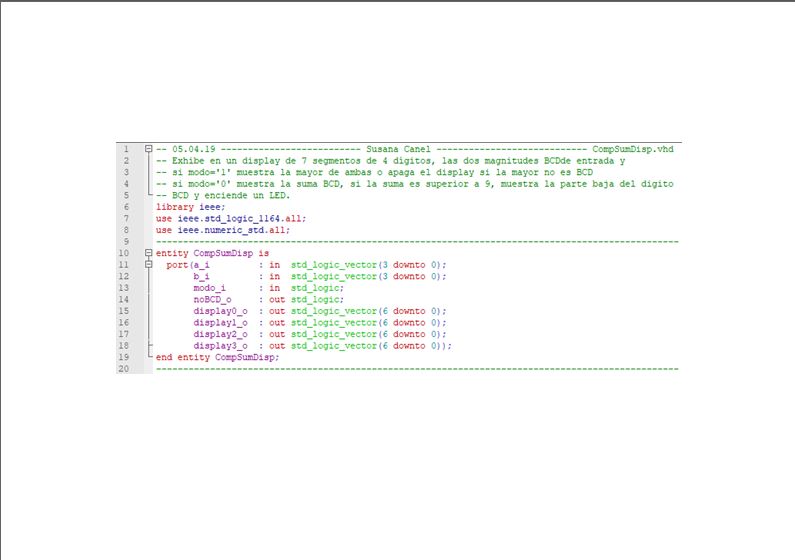

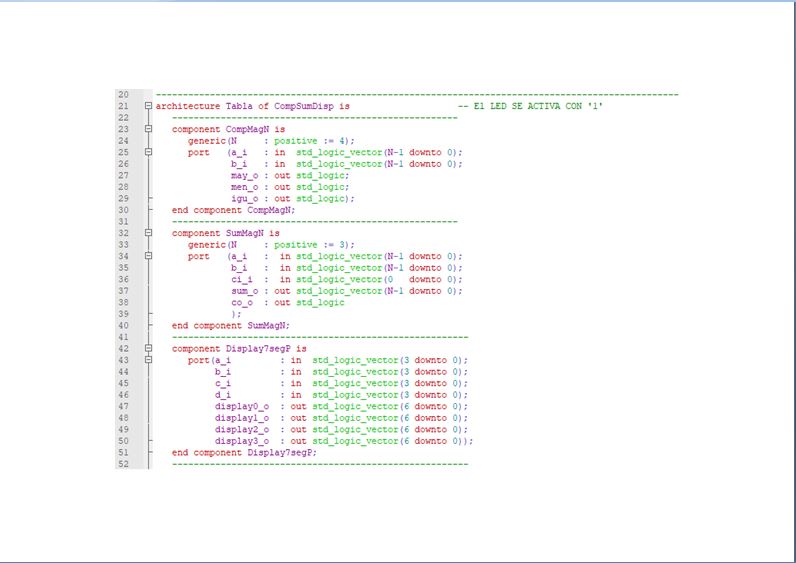

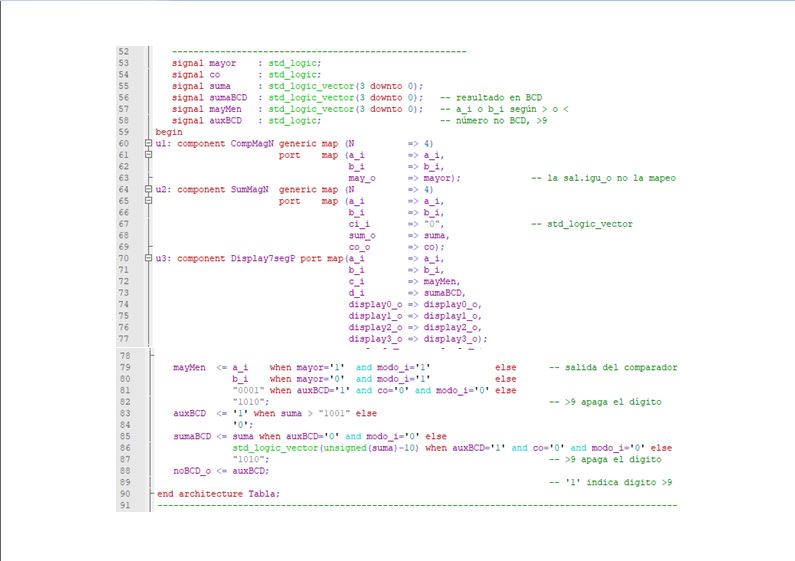

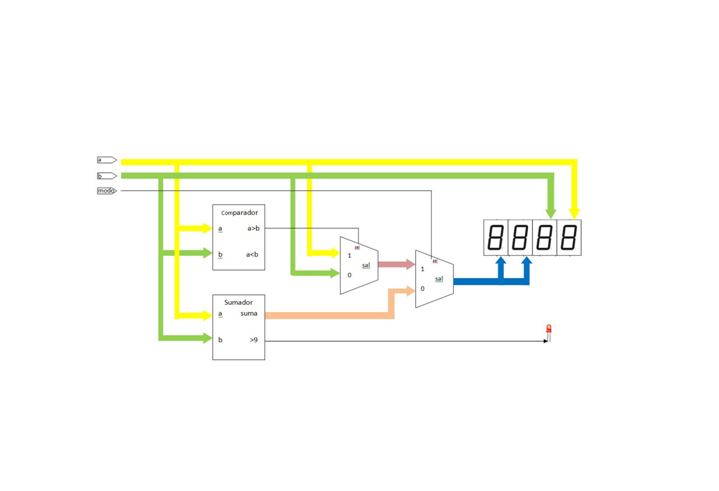

Lección 5. VHDL estructural para la plaqueta.

Descripción de un circuito para usar en la plaqueta DE1 de Altera. Control de un display de 7 segmentos de 4 dígitos. Al circuito entran dos señales BCD de 4 bits y una señal de modo. La salida son los 4 dígitos de un display de 7 segmentos, en los que se exhiben los datos de entrada, el mayor de ellos y el resultado de la suma. Y un indicador de si la suma está entre 10 y 15 (no es BCD). Muestro el RTL Viewer.

Lección 5.V25.2. Hardware sintetizado y efectos de eliminación de una señal de la descripción.

En este video analizo el RTL y el Technology Map Viewers comparándolos con la descripción VHDL y explicando que son los LE (Logic Element) y la LUT ( look-up-table) y cómo verlos en el Technology Map. Modifico la descripción eliminando una señal y muestro los efectos sobre el hardware sintetizado y los tiempos de propagación de las señales. Muestro las etapas del diseño CAD. Muestro como se asignan las patas. Explico la diferencia entre programar y configurar. Muestro cómo se usa el programador del Quartus II, para configurar la FPGA. Archivo de extensión SOF para bajar a la SRAM del Cyclone II.

Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Análisis el RTL y el Technology Map Viewers

Lección 5.V25.1. Descripción de un circuito que maneja hardware.

Descripción de un circuito para usar en la plaqueta DE1 de Altera. Se trata de manejar el display de 7 segmentos de 4 dígitos de la plaqueta. Al circuito entran dos señales BCD de 4 bits y una señal de modo. La salida son los 4 dígitos de un display de 7 segmentos, en los que se exhiben los datos de entrada, el mayor de ellos y el resultado de la suma. Y un indicador (un LED) de si la suma está entre 10 y 15 (no es BCD). Muestro el RTL Viewer. Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Lección 5.V24. Descripción estructural de un circuito.

En este video vemos la descripción VHDL de un circuito usando arquitectura estructural. Instancio componentes. Genero una library y un package propios. Informo al Quartus que voy a usar mi library y mi package y las descripciones de los componentes. Vemos los circuitos sintetizados por RTL Viewer y Technology Map Viewer, comparándolos con el circuito y con la tabla de verdad y ecuaciones del circuito. Puedes ver el código en mi post Lección 5. VHDL descripción estructural. /blog/page/3/ A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

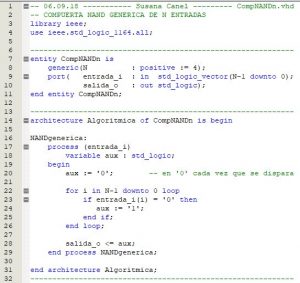

Lección 4.V23. Descripción NAND genérica.

Puedes ver el código en mi post Lección 4. VHDL descripción algorítmica. /2018/09/03/leccion-4-arquitectura-algoritmica/ . A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

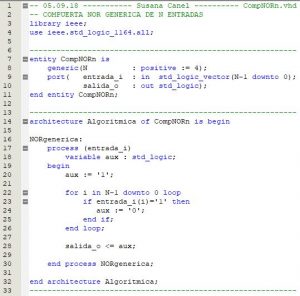

Lección 4.V22. Descripción NOR genérica.

Descripción VHDL, usando arquitectura algorítmica de una compuerta NOR genérica, de N bits. este tipo de arquitectura por ser secuencial ncesita del uso de procesos explícitos, process. El proceso contiene solamente sentencias secuenciales y procesos implícitos de asignación simple. En este ejemplo uso las sentencias for…loop e if. Defino una variable auxiliar. Muestro el RTL Viewer y el Technology Map Viewer, generados. Simulo para comprobar el correcto funcionamiento. Como introducción sintetizo lo visto hasta el momento: arquitecturas por comportamiento y los diferentes estilos. Puedes ver el código en mi post Lección 4. VHDL descripción algorítmica. /2018/09/03/leccion-4-arquitectura-algoritmica/ . A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/

Lección 4. Arquitectura algorítmica.

Descripción VHDL, usando arquitectura algorítmica de una compuerta NOR genérica, de N bits. este tipo de arquitectura por ser secuencial necesita del uso de procesos explícitos, process. El proceso contiene solamente sentencias secuenciales y procesos implícitos de asignación simple. En este ejemplo uso las sentencias for…loop e if. Defino una variable auxiliar. Muestro el RTL Viewer y el Technology Map Viewer, generados. Simulo para comprobar el correcto funcionamiento. Como introducción sintetizo lo visto hasta el momento: arquitecturas por comportamiento y los diferentes estilos.

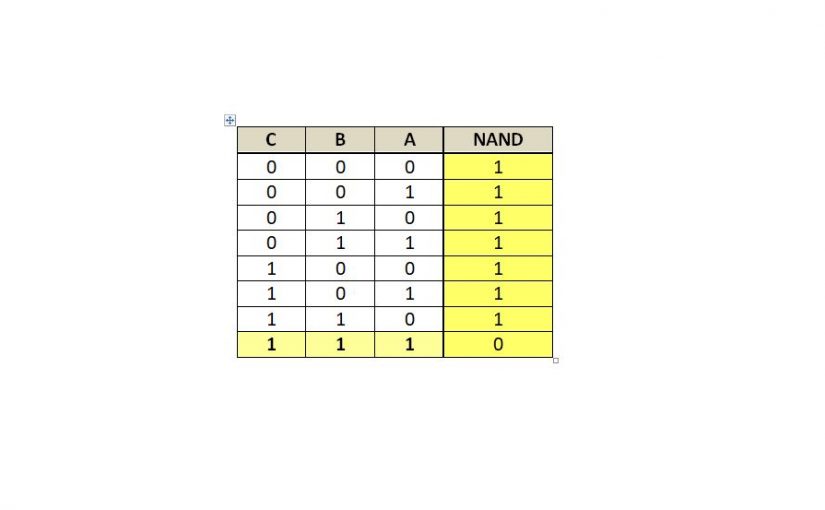

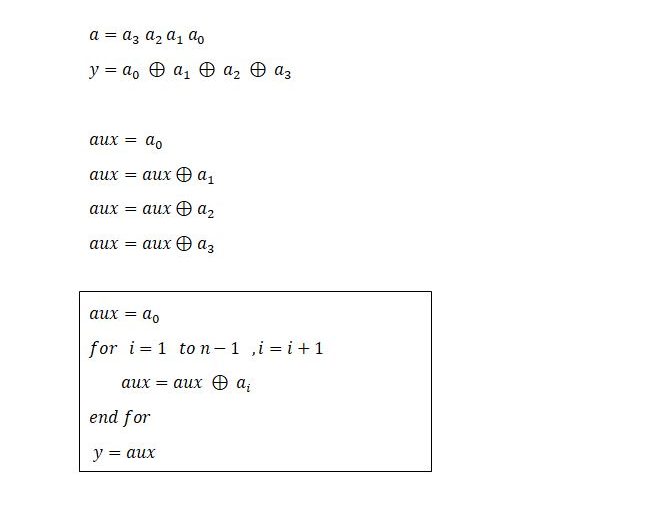

Lección 3.V21. Árbol de paridad genérico.

Descripción VHDL de un árbol de paridad genérico, de N bits. Defino un proceso explícito, process y una variable. Uso una sentencia secuencial for…loop. Comento la diferencia entre señales y variables y entre procesos implícitos y explícitos. Uso una etiqueta, label. Te muestro el RTL Viewer y el resultado de la simulación. Puedes ver el código en mi post Lección 3. VHDL por comportamiento. /blog/page/6/. A través de “contactame” puedes pedirme que te envíe los archivos de texto con las descripciones para que los puedas probar y el tutorial del Quartus II, que hice. /contactame/