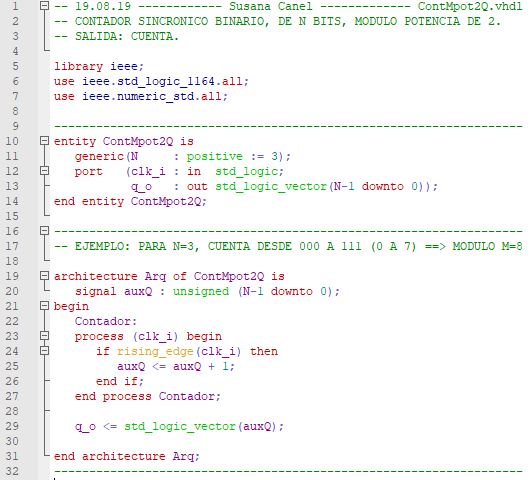

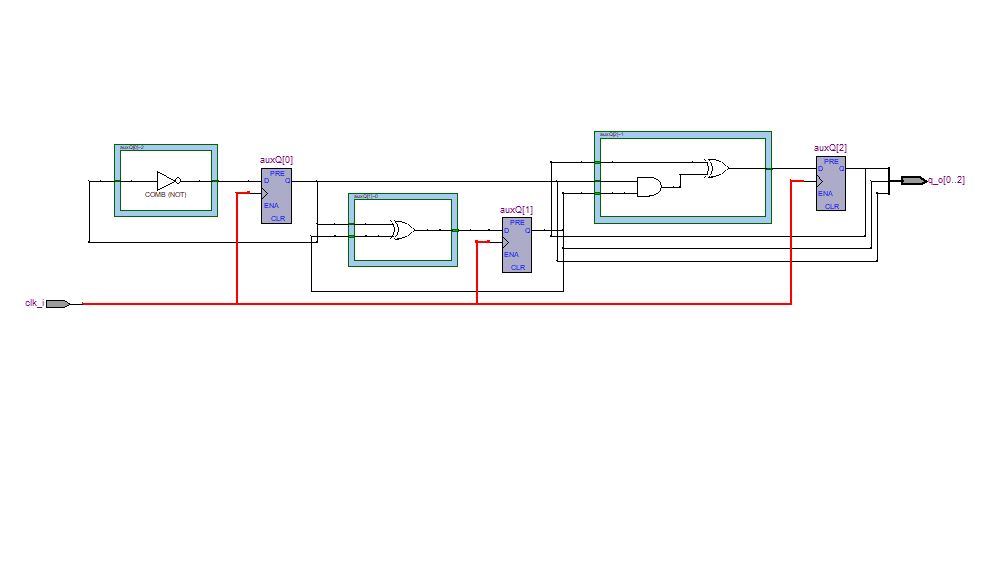

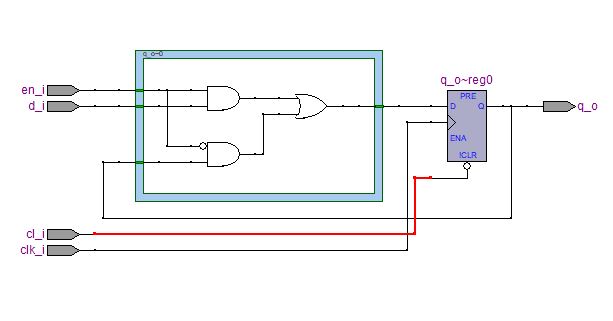

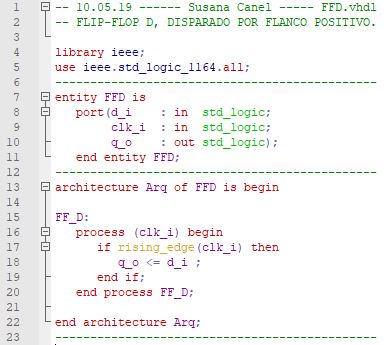

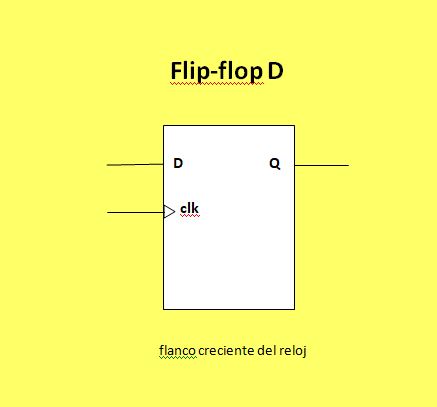

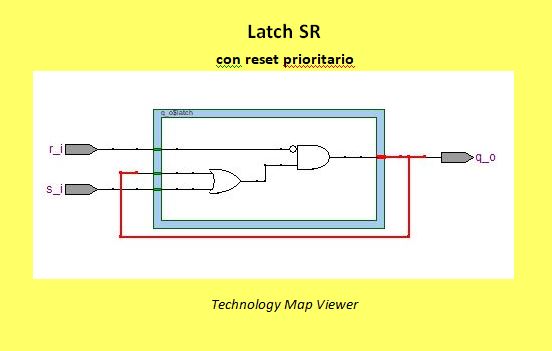

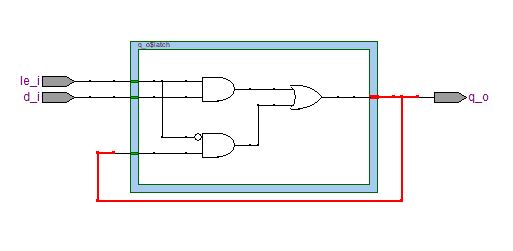

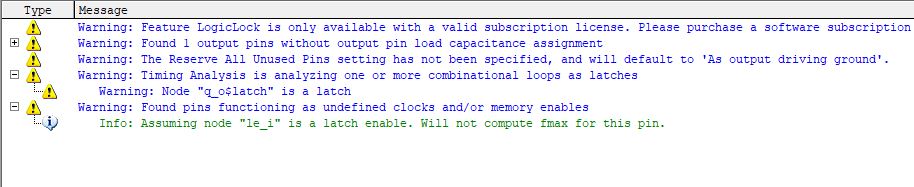

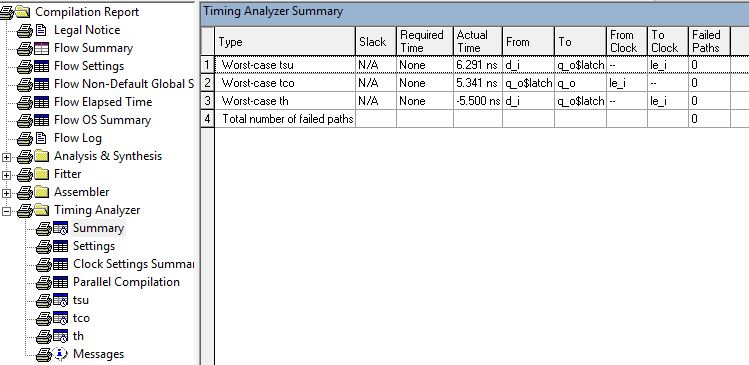

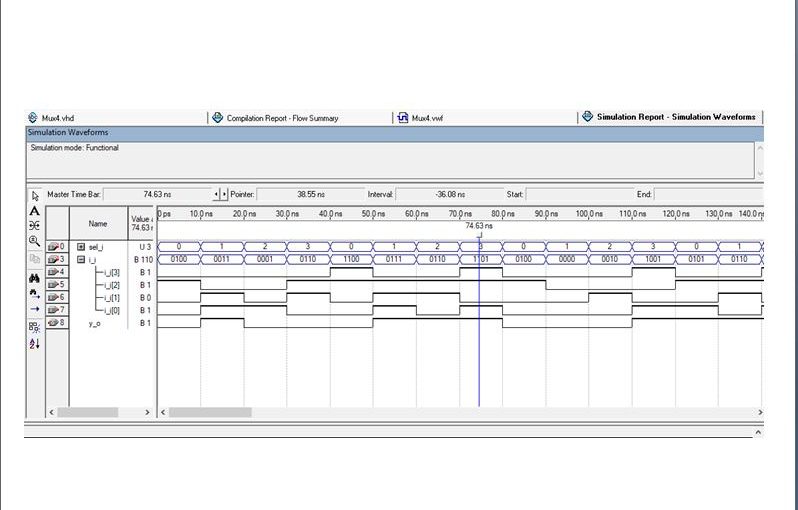

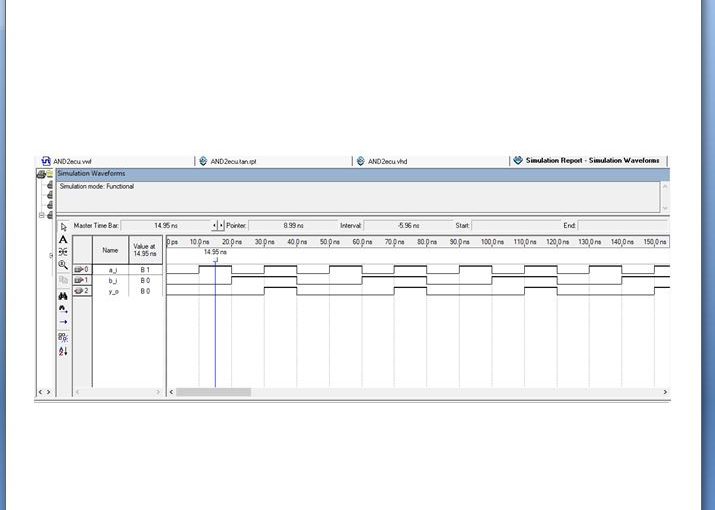

En este video te explico la descripción VHDL de un contador binario de módulo potencia de 2, también llamado cíclico. Como primer ejemplo elegí un contador que tiene solamente la entrada de pulsos a contar (reloj) y como salida el estado de la cuenta. Como uso una señal de tipo unsigned incluyo el package numeric_std. Uso la función rising_edge. Compilo y controlo los “warnings”. Luego recurro a la herramienta “Tool” y selecciono “Technology Map Viewer” del Quartus II para ver y analizar el circuito esquemático generado.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/ .