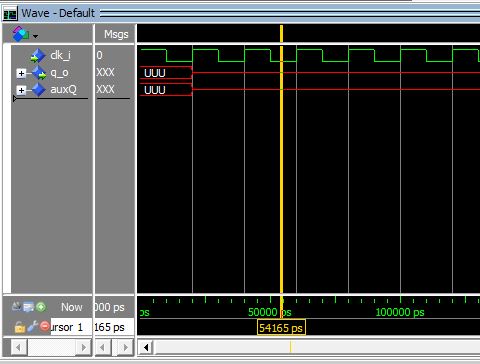

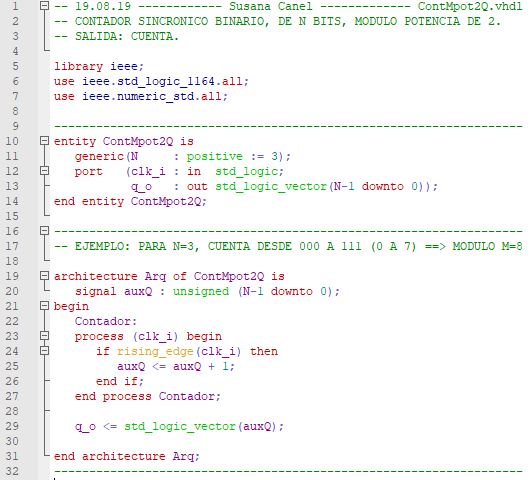

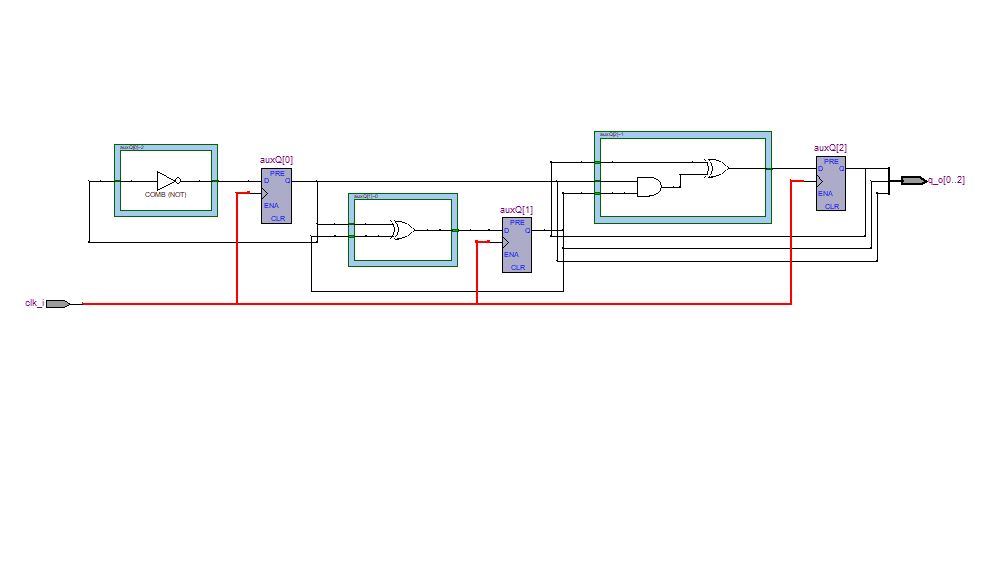

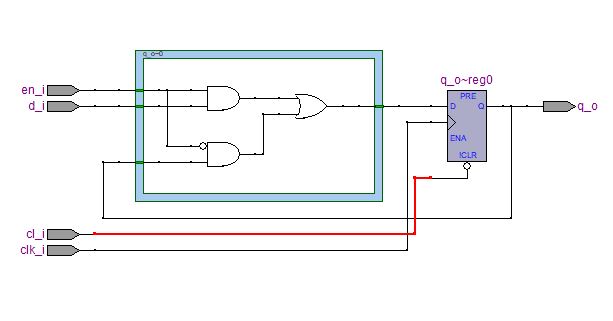

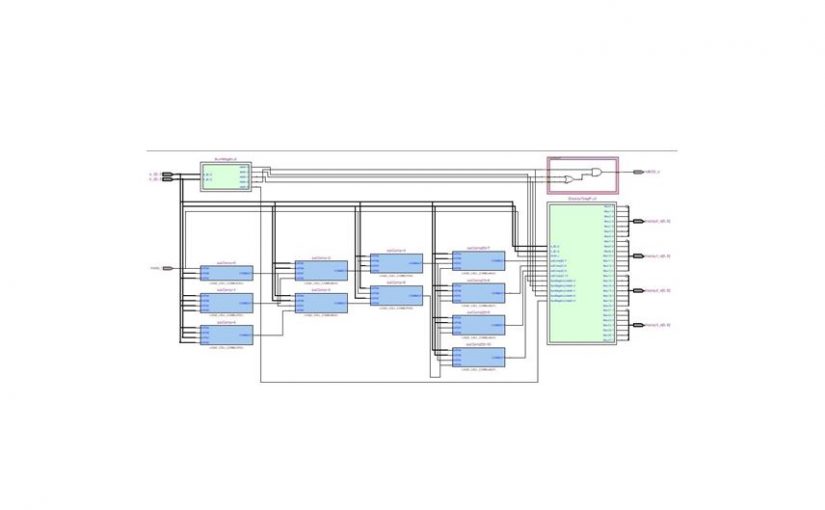

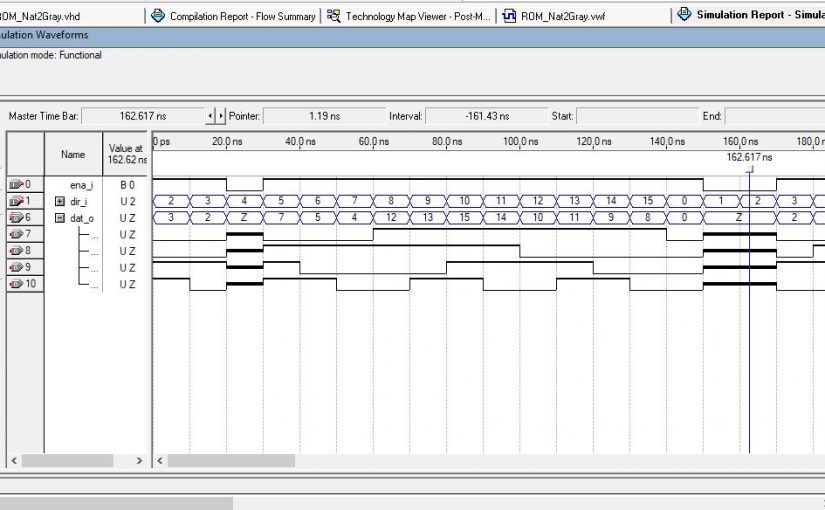

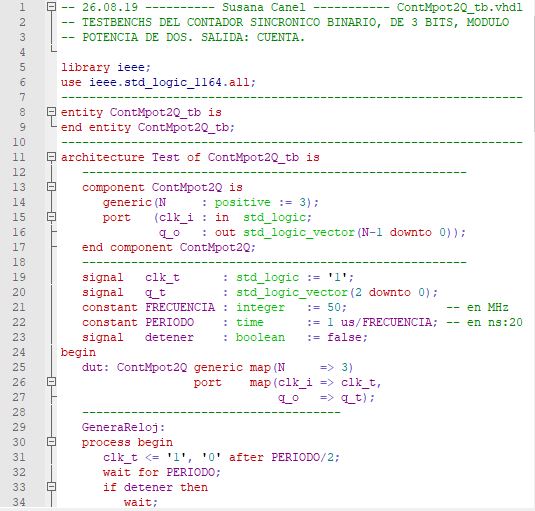

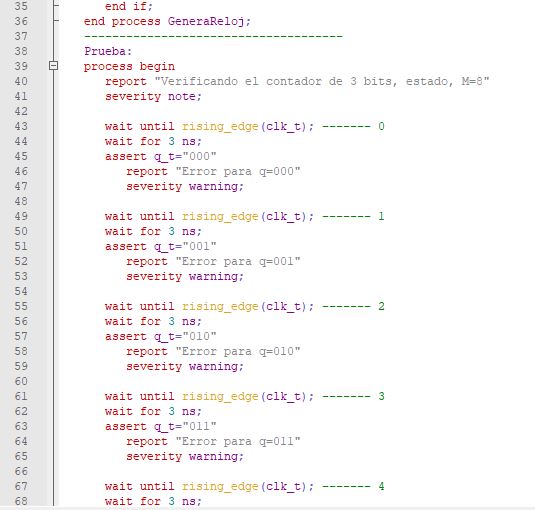

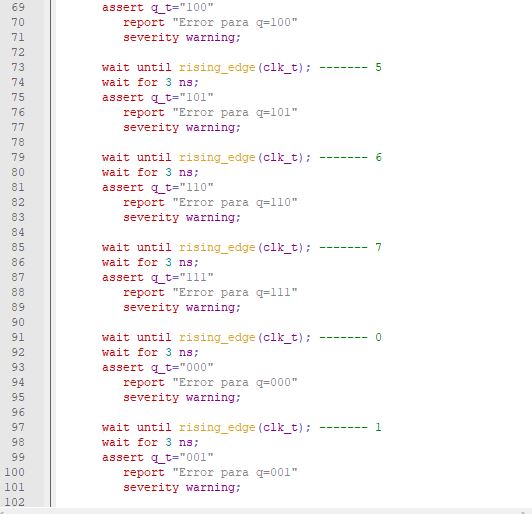

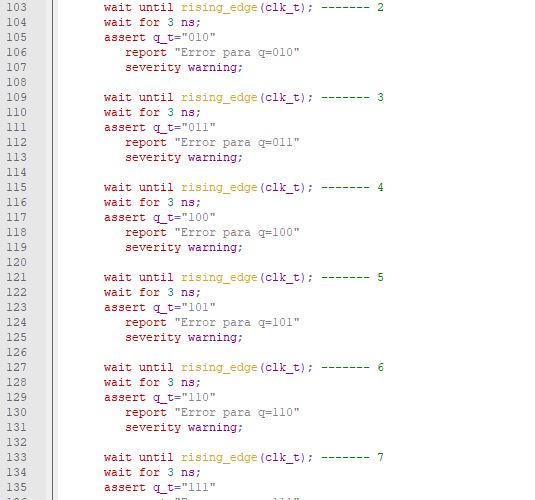

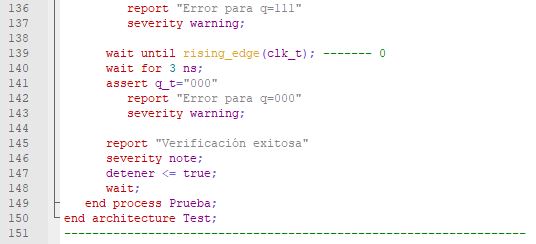

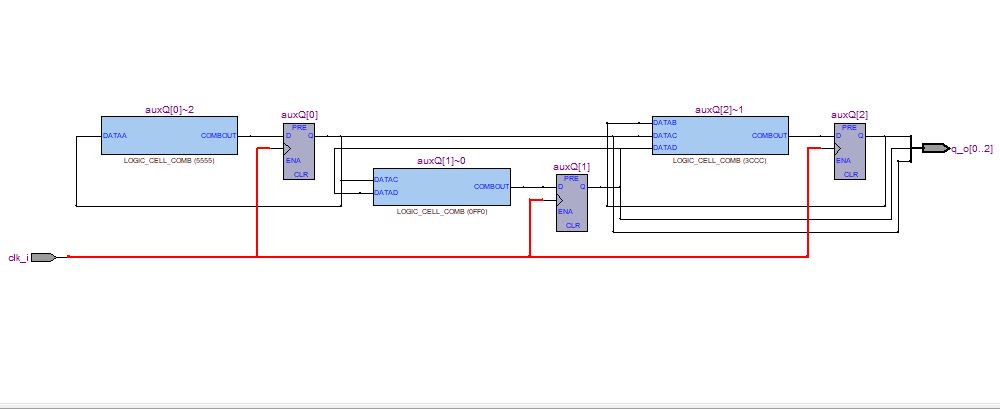

En este video te explico el testbench para el contador elemental del video anterior. Se trataba de un contador con solo señal de pulsos a contar y la salida del estado de la cuenta. Te explico los problemas que se generan al no partir de un estado inicial conocido. Te muestro el testbench interactuando con la descripción. También analizo qué sucede en el hardware cuando no hay un estado inicial mirando el circuito generado por la herramienta “Technology Map Viewer” del Quartus II.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/ .

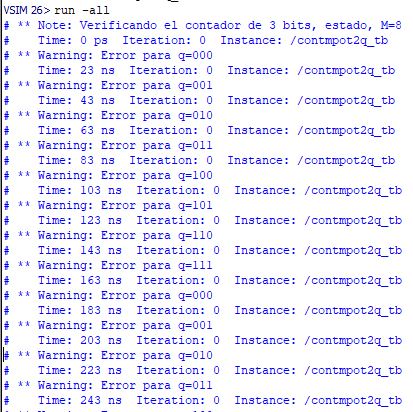

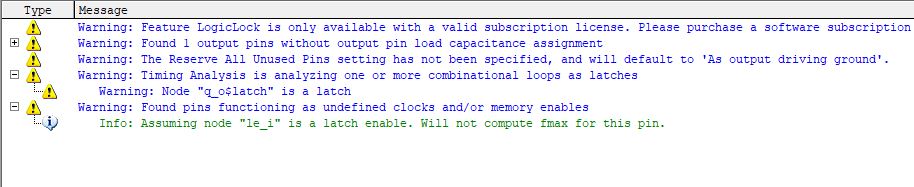

Salida de la ventana “transcript” luego de la simulación en el ModelSim.