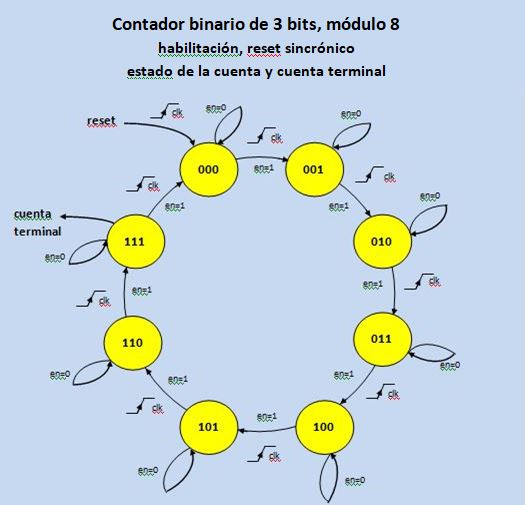

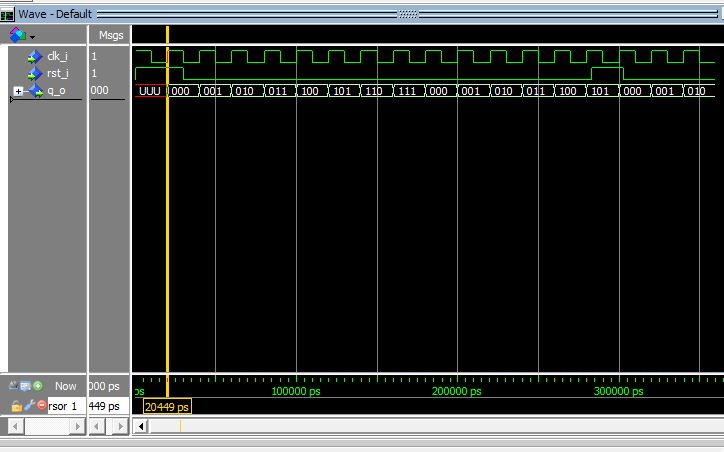

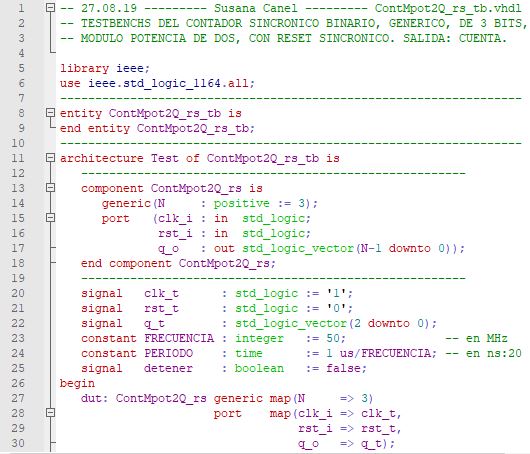

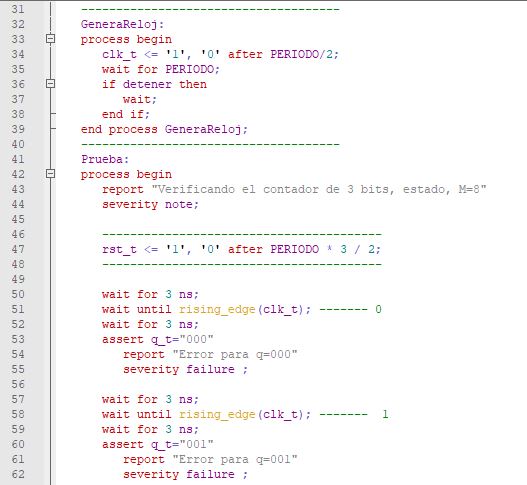

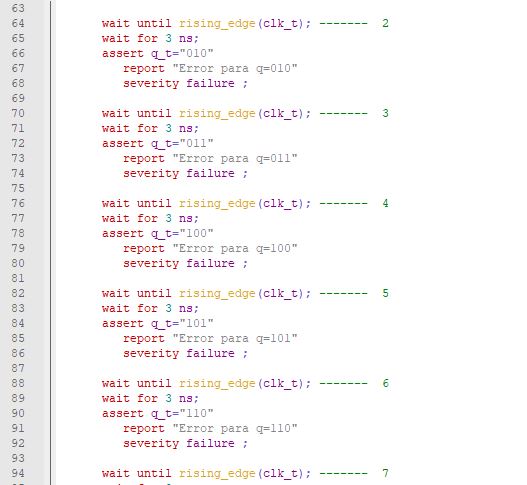

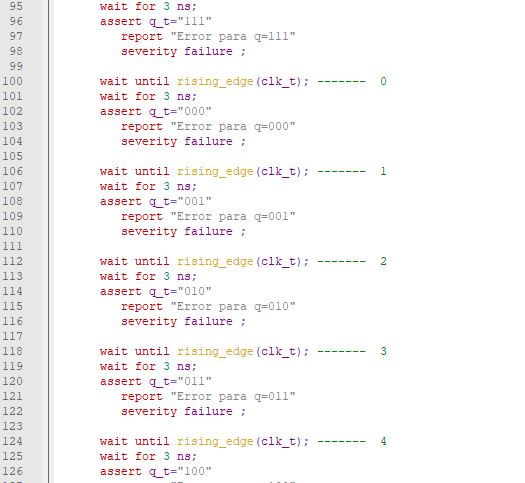

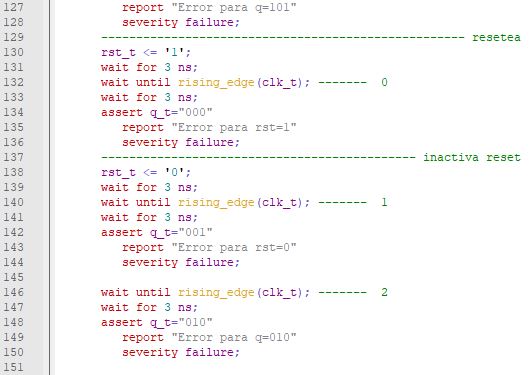

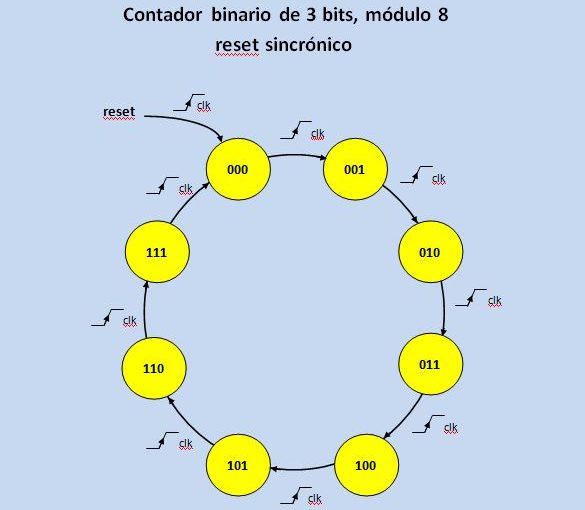

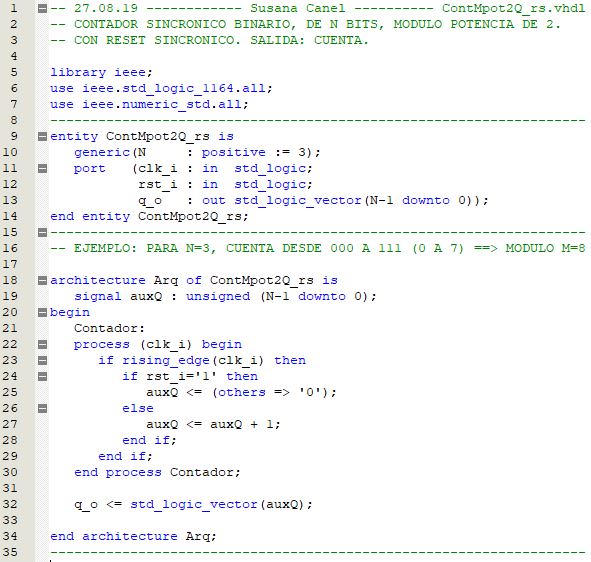

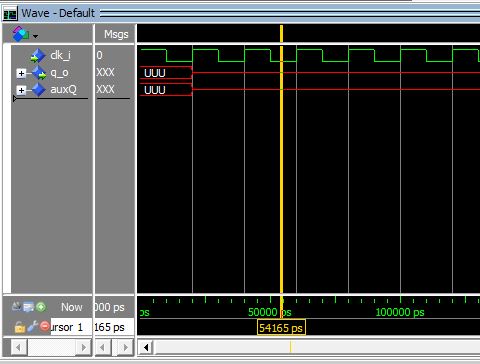

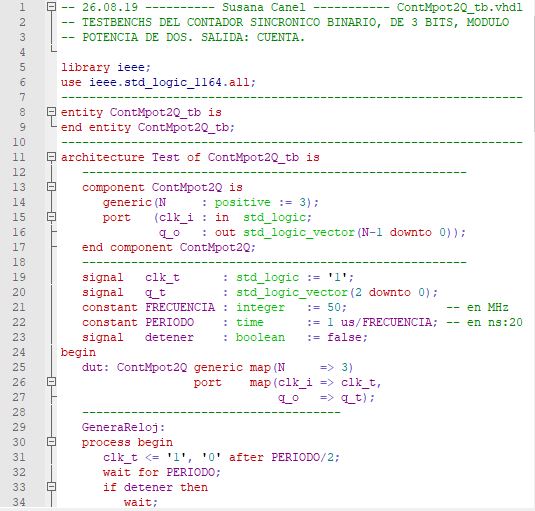

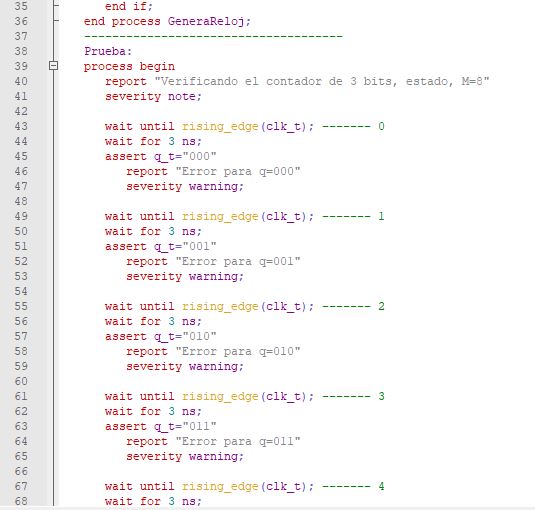

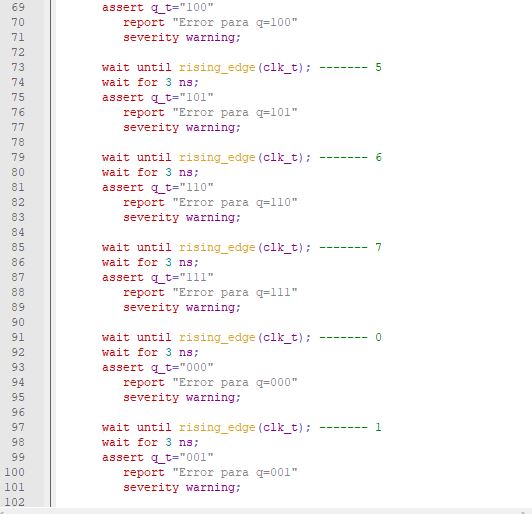

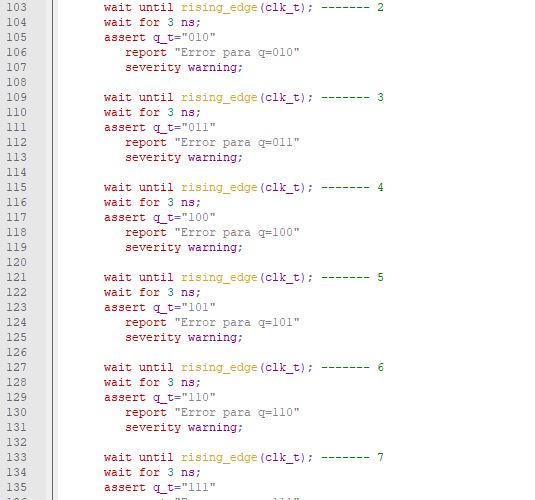

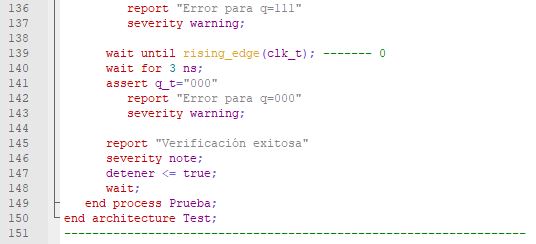

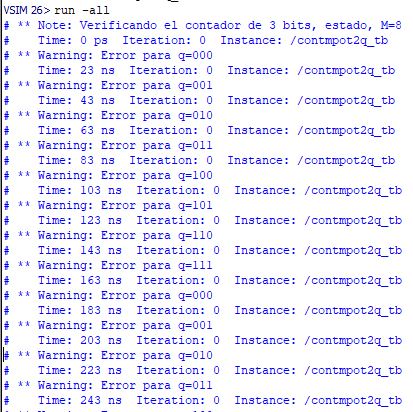

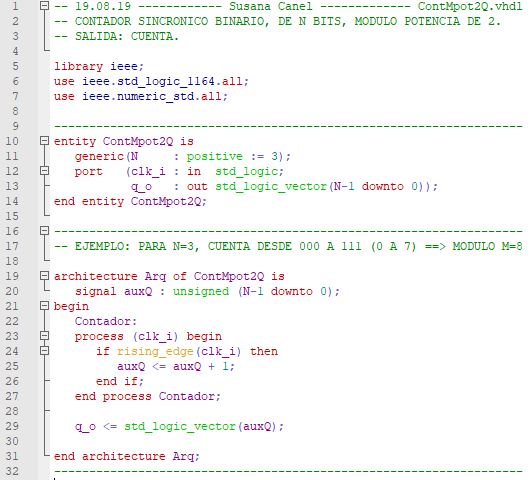

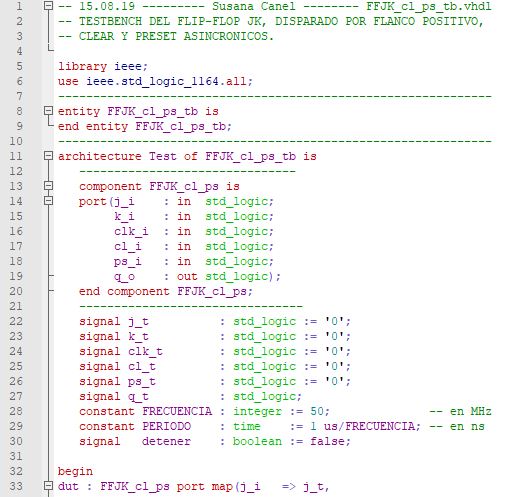

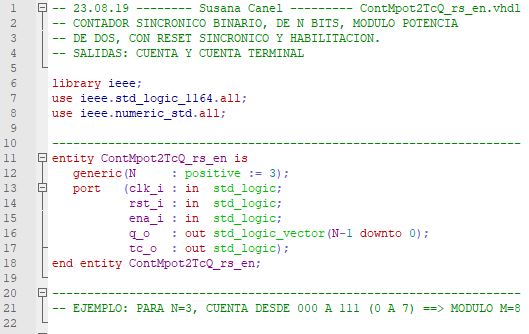

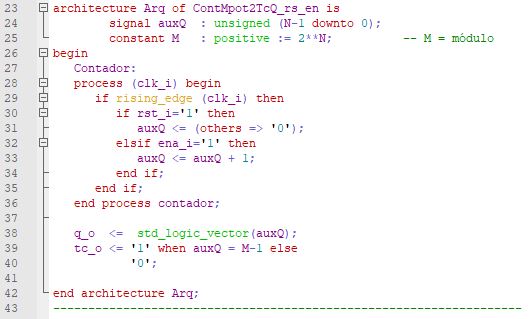

En este video te explico la descripción de un contador genérico, sincrónico, binario, de módulo potencia de 2, con salidas: cuenta terminal y estado (valor de la cuenta). Analizo una sentencia que en la simulación va a producir un “Warning: metavalue detected”. Analizo el circuito generado.

Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/.

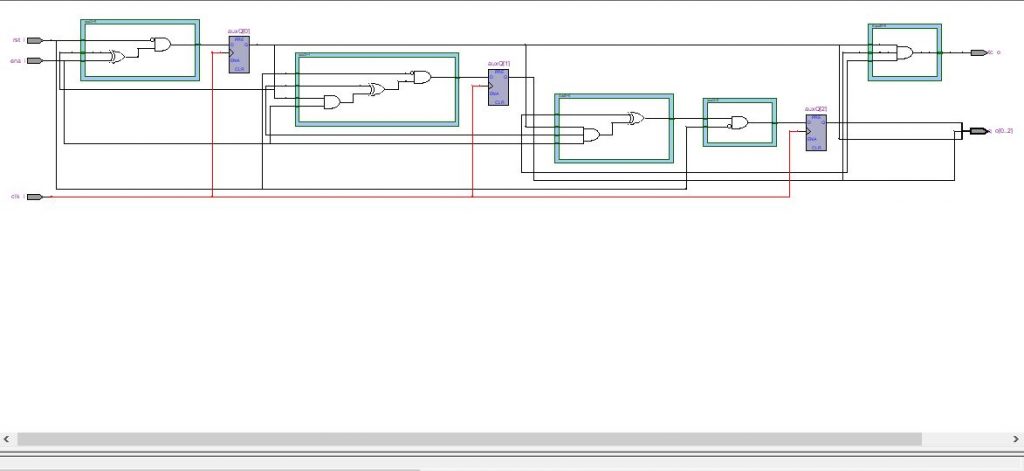

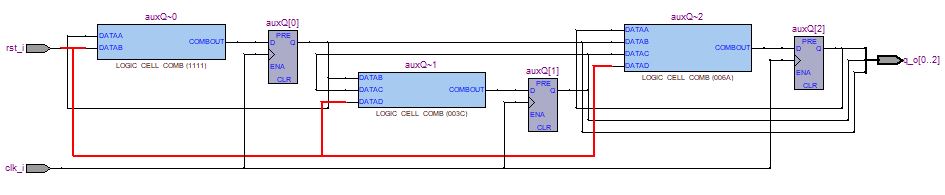

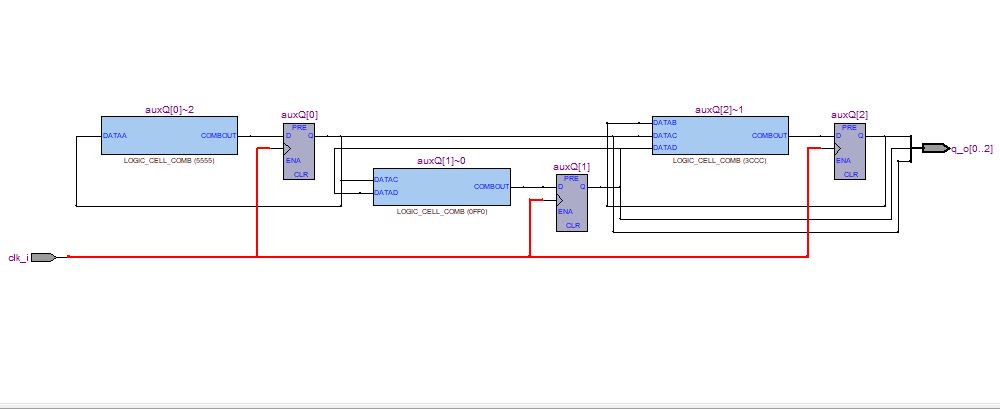

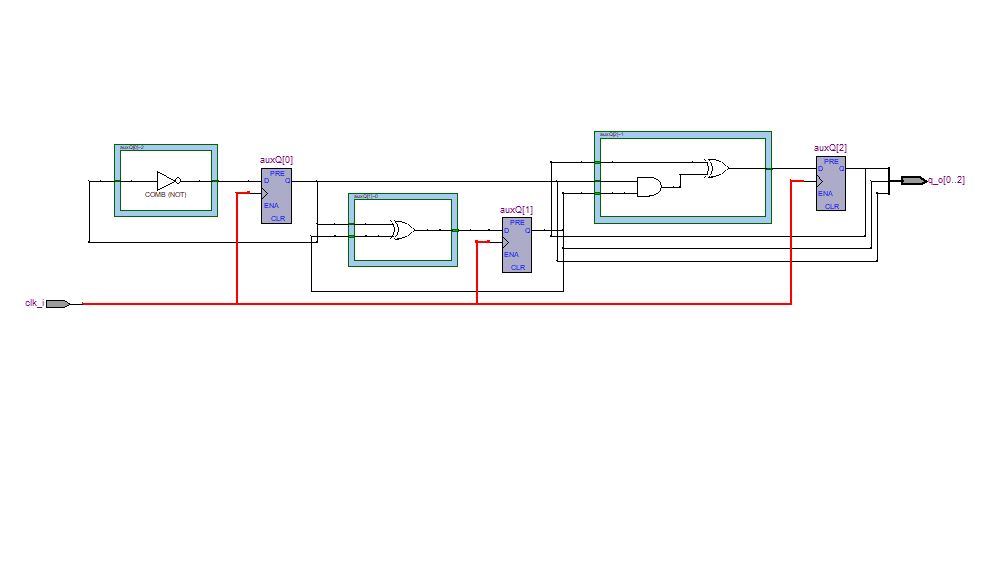

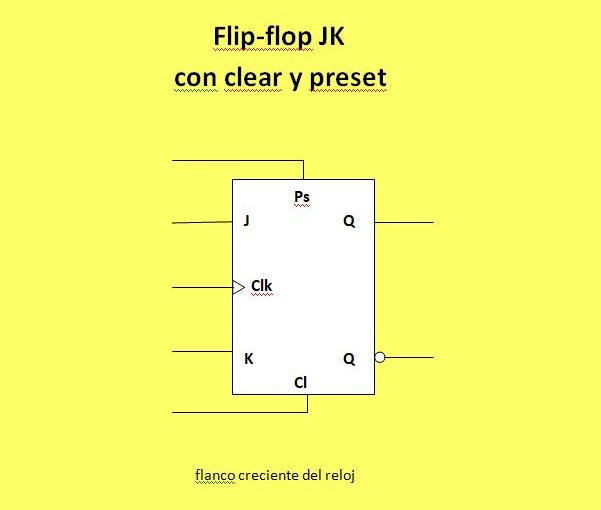

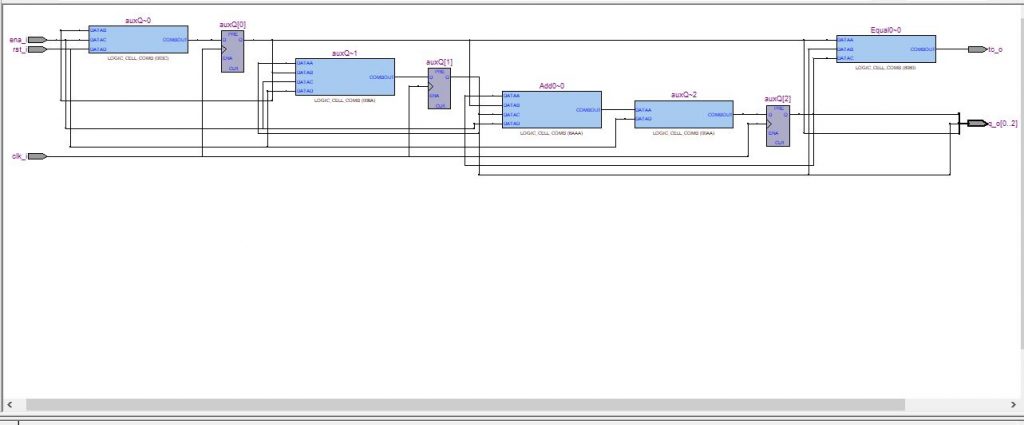

Esquema circuital producido por Technology Map Viewer.

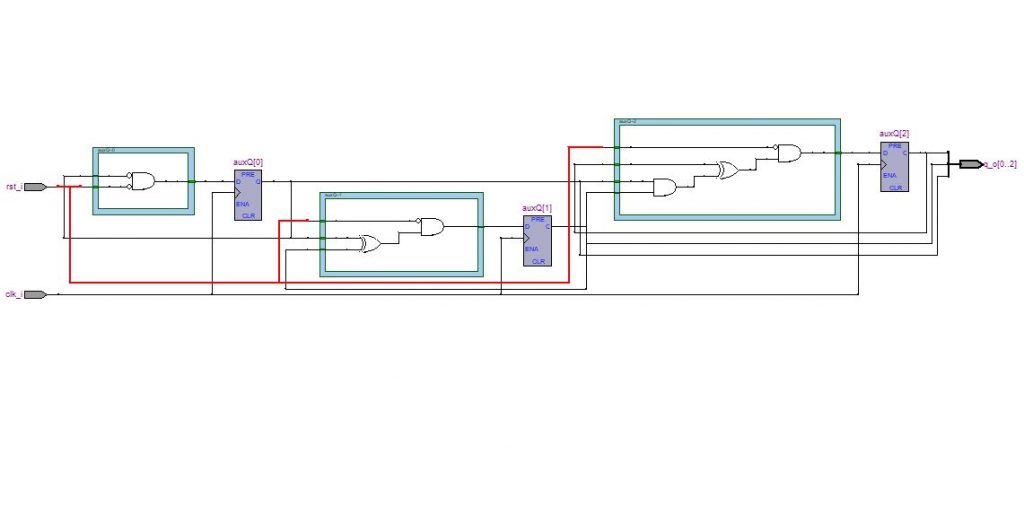

Detalle de las celdas lógicas combinacionales.