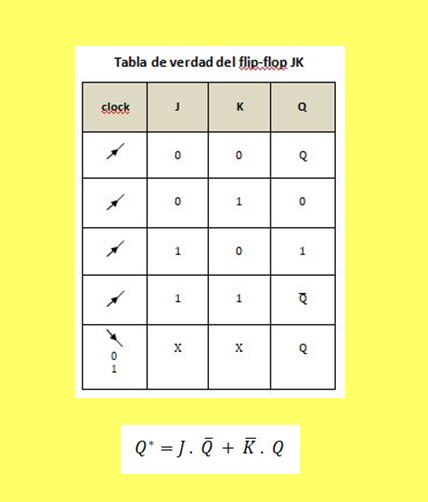

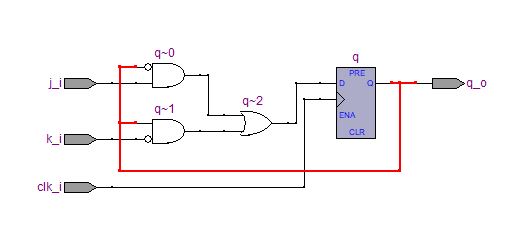

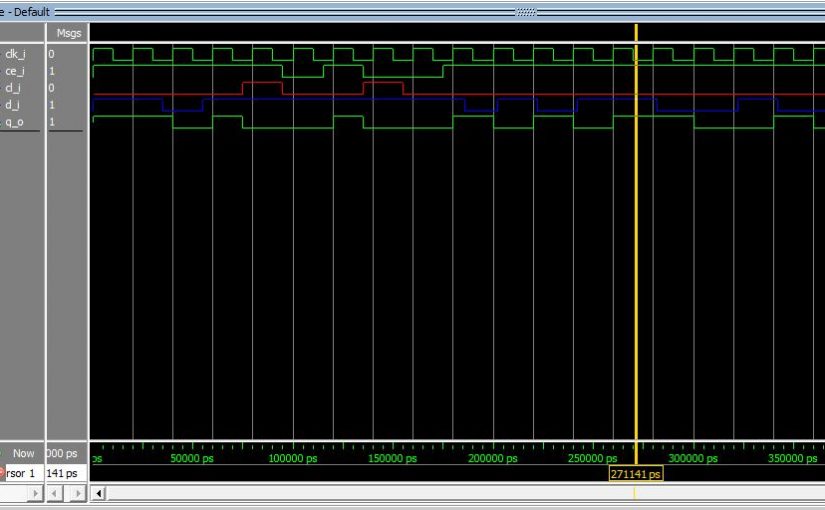

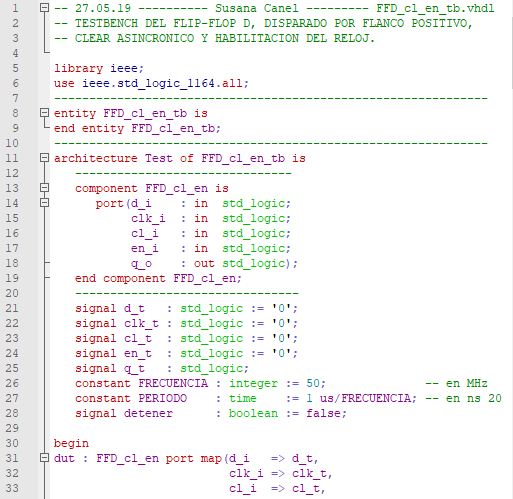

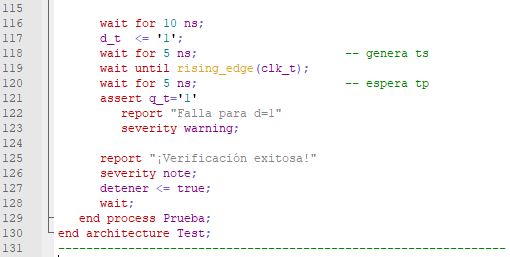

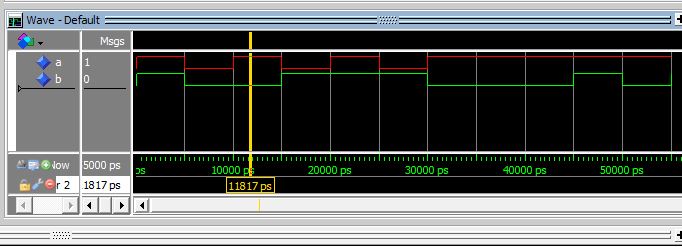

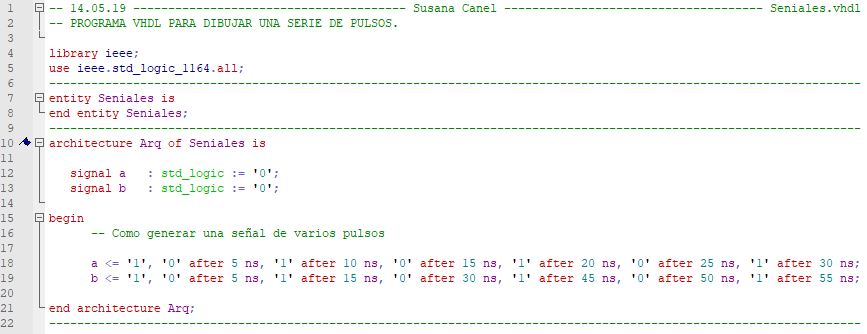

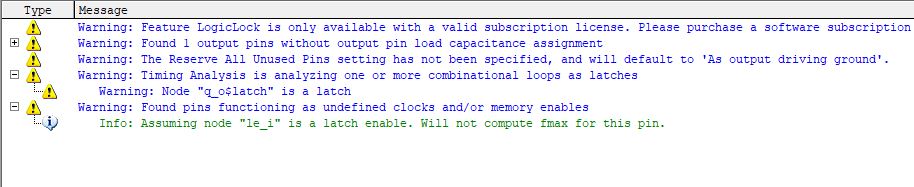

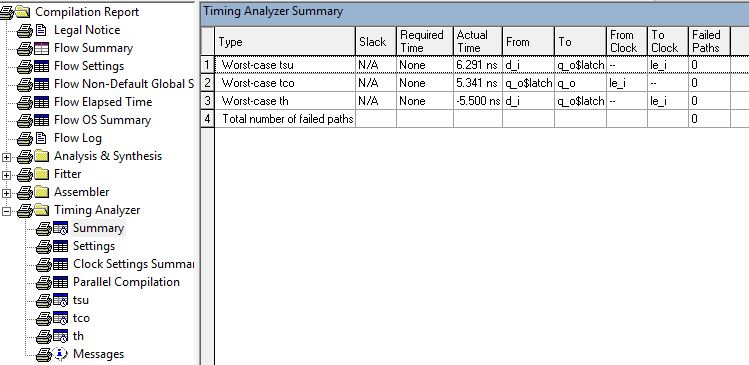

En este video te explico cómo describir un flip-flop JK a partir de su ecuación característica. Uso la función rising_edge para detectar el flanco creciente de la señal de reloj. En la arquitectura defino una señal auxiliar para poder escribir la ecuación característica del flip flop. Compilo y analizo un warning. Luego recurro a la herramienta Tool del Quartus y selecciono RTL Viewer para ver y analizar el circuito esquemático generado. Si te parece útil la explicación no te olvides de darle un clic a “me gusta” ¡Gracias! Para contactarme y solicitarme los manuales del Quartus II que escribí en español en lenguaje amigable (no son una traducción) y también los archivos de las descripciones y testbenchs en formato texto para que los puedas probar, entra en /contactame/ .